## UNIT-I

## LOW – FREQUENCY SINGLE – STAGE AMPLIFIERS

## **Objectives**

- To introduce basic structures of MOSFET and BJT amplifier circuits.

- To familiarize with characteristic parameters of amplifiers

- To design and analyse behaviour of BJT & FET amplifiers at low frequencies.

# **Syllabus**

MOS Amplifiers, The basic structure, characterizing MOS amplifiers, low - frequency response of common source (CS) amplifier, common source (CS) amplifier with a source resistance, design of CS amplifier, BJT amplifiers, The basic structure, characterizing BJT amplifiers, low – frequency response of the common emitter (CE) amplifier, common emitter (CE) amplifier with an emitter resistance, design of CE amplifier.

# **Pre-requisites**

- Small-signal models of MOSFET

- Small-signal models of BJT

- Circuit models for amplifiers

- The terms: Frequency response and Bandwidth of an amplifier

# **Outcomes:**

Students will be able to

- distinguish unilateral and non-unilateral amplifiers

- analyse FET and BJT amplifiers at low frequencies

- design CE and CS amplifiers at low frequencies

# **Pre-requisites**

• Small – signal equivalent circuit models of MOSFET

- From a signal point of view the FET behaves as a Voltage Controlled current source. It accepts a signal V<sub>GS</sub>between gate and source and provides a current g<sub>m</sub>V<sub>GS</sub>, at the drain terminal.

- The input resistance of this controlled source is very high ideally infinite. The output resistance i.e., resistance looking in to the drain also is high.

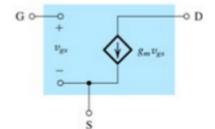

- Putting all of this together, we get the circuit in as shown in below figure that represents the small signal model or small signal equivalent circuit.

Fig. Small signal model for the MOSFET neglecting the dependence of i<sub>D</sub> on V<sub>DS</sub> in saturation

- In the analysis of a MOSFET amplifier circuit, transistor can be replaced by the equivalent model. Ideal constant DC voltage sources are replaced by short circuit, and Ideal constant DC current sources are replaced by an open circuit in the small signal model.

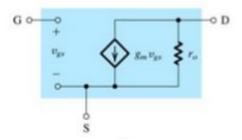

- Another approach of the small signal model of amplifier is that assume the drain current in saturation is independent of the drain voltage. From MOSFET characteristics in saturation, we know that the drain current does in fact depend on V<sub>DS</sub> in linear manner. Such linear relation was modeled by a finite resistance r<sub>o</sub> between drain and source. we represent it as

$$r_o = \frac{|V_A|}{I_D}$$

The current I<sub>D</sub> is the value of the DC drain current without the channel –length modulation taken into account ; that is,

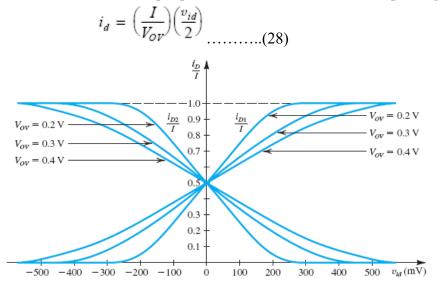

$$I_D = \frac{1}{2} k'_n \frac{W}{L} V_{OV}^2$$

Accuracy of the small signal model can be improved by including r<sub>o</sub> in parallel with the controlled source.

## Fig.Small signal model for MOSFET including the effect of channel –length modulation.

- > It is important to note that small signal model parameters  $g_m$  and  $r_o$  depend on the DC bias point of the MOSFET.

- MOSFET amplifier voltage gain expression

$$A_v = \frac{v_d}{v_{gs}} = -g_m (R_D //r_o)$$

- > Thus finite output resistance  $r_o$  results in a reduction in the magnitude of voltage gain.

- All the above analysis performed on an NMOS transistor, apply equally well to PMOS device, except for using  $V_{GS}$ ,  $V_t$ ,  $V_{OV}$ , and  $V_A$  and replacing  $k_n$ ' with  $k_p$ '.

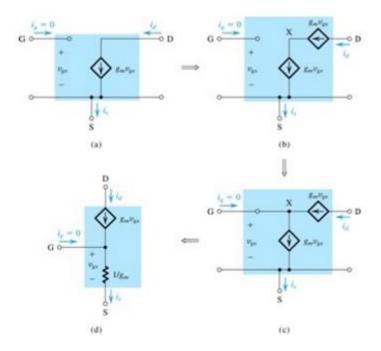

## The T Equivalent Circuit Model

- It is possible to develop an alternate equivalent circuit model for the MOSFET. The development of such model is known as T model.Figure (a) shows the equivalent circuit of MOSFET without r<sub>o</sub>.

- > In the figure as shown below, we have added a second  $g_m V_{gs}$  current source in series with the original controlled source. This addition of current source does not change the terminal currents.

- The newly created circuit node, labeled as X, is joined to the gate terminal G. Observe that the gate current doesn't change(remains equal to zero)-thus this connection doesn't alter the terminal characteristics.

- We have a controlled voltage source  $g_m v_{gs}$  connected across its control voltage vgs. We can replace this controlled source by a resistance as long as this resistance draws an equal current as the source. Thus the value of resistance is  $v_{gs}/g_m v_{gs} = 1/g_m$ . This replacement is shown in figure (d)

- Observe that ig is still zero, id = gmvgs and is=vgs/(1/gm) = gmvgs, all same as the original model in figure (c)

- Note that the resistance between gate and source, looking into the gate, is infinite. This observation useful in many applications.

Fig.Development of the T equivalent – circuit model for the MOSFET. For simplicity,  $r_0$  has been omitted but can be added between D and S in the T model of (d).

> In T-model including resistance  $r_0$  between drain and source the circuit is modeled as follows.

Fig.(a)The T model of the MOSFET augmented with the drain to source resistance  $r_{0}$ ; (b) An alternative representation of the T model.

• Small signal equivalent circuit models of BJT

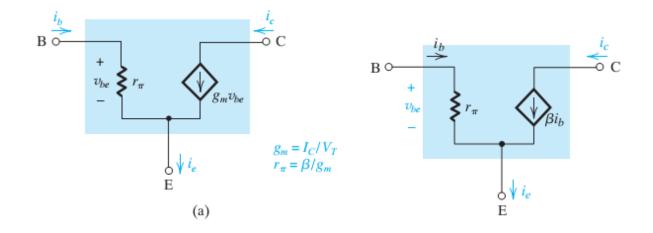

## The Hybrid $-\pi$ Model

An equivalent circuit model for the BJT is shown in below fig

Fig. Two slightly different versions of the simplified hybrid  $-\pi$  model for the small signal operation of the BJT. The equivalent circuit in (a) represents the BJT as a voltage controlled current source (a transconductance amplifier), and that in (b) represents the BJT as a current controlled current source (a current amplifier).

- Model (a) represents the BJT as a voltage controlled current source and explicitly includes the input resistance looking into the base  $r_{\pi}$ . The model obviously yields  $i_c = g_m v_{be}$  and  $i_b = v_{be}/r_{\pi}$ .

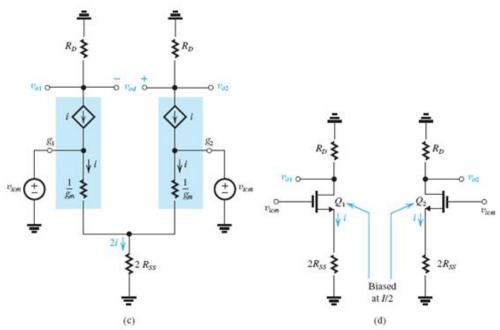

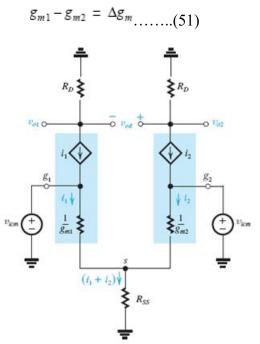

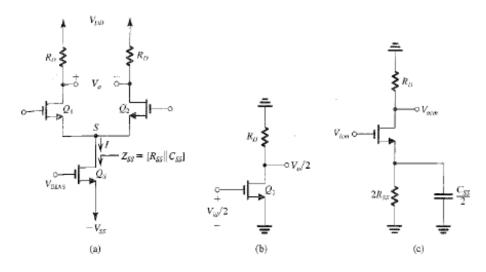

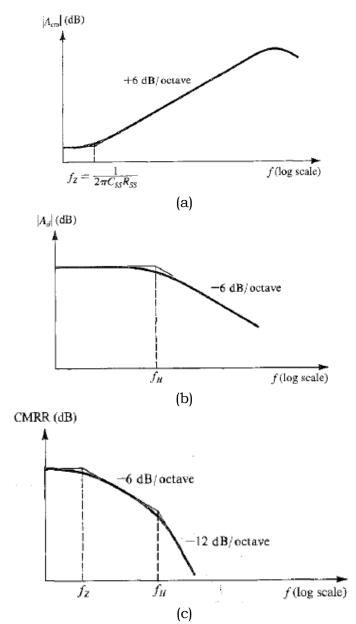

- ➤ At the emitter node we have

$$i_e = \frac{v_{be}}{r_{\pi}} + g_m v_{be} = \frac{v_{be}}{r_{\pi}} (1 + g_m r_{\pi})$$

$$= \frac{v_{be}}{r_{\pi}} (1 + \beta) = v_{be} / \left(\frac{r_{\pi}}{1 + \beta}\right)$$

$$= v_{be} / r_e$$

A slightly different circuit model(b) can be obtained by expressing the current of the controlled source (g<sub>m</sub>v<sub>be</sub>) in terms of the base current i<sub>b</sub>(current controlled current source ) as follows:

$$g_m v_{be} = g_m (i_b r_\pi)$$

=  $(g_m r_\pi) i_b = \beta i_b$

- The two models (a & b) are the simplified hybrid  $-\pi$  model for the small signal operation for the BJT. The model parameters  $g_m$ ,  $r_{\pi}$  depend on the value of the DC bias current Ic.

- Finally, although the models have been developed for an NPN transistor, they apply equally well to a PNP transistor with no change of polarities.

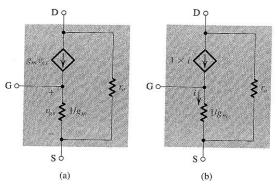

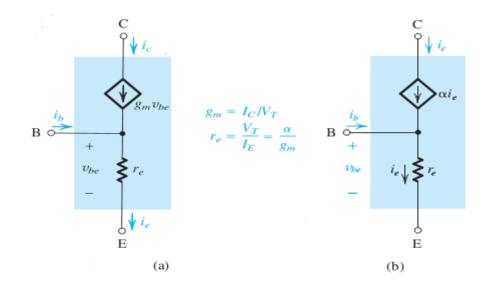

#### The T Model

> Although hybrid  $-\pi$  model can be used to carry out small signal analysis of all transistor circuits, there are situations in which alternative model shown in below fig, is much more convenient, is called as T model.

Fig. Two slightly different versions of what is known as the T model of the BJT. The circuit in (a) is a voltage controlled current source representation and that in (b) is a current controlled current source representation. These models explicitly show the emitter resistance  $r_e$  rather than the base resistance  $r_{\pi}$  featured in the hybrid  $-\pi$  model.

- The two versions of T-model shown in above figure. Fig. (a) represents the BJT as a voltage controlled current source with the control voltage being v<sub>be</sub>. Here, however, the resistance between base and emitter, looking into the emitter, is explicitly shown.

- From fig(a) we see clearly that the model yields the correct expression for i<sub>c</sub> and i<sub>b</sub>. For i<sub>b</sub> we note that at the base node we have

$$i_b = \frac{v_{be}}{r_e} - g_m v_{be} = \frac{v_{be}}{r_e} (1 - g_m r_e)$$

$$= \frac{v_{be}}{r_e} (1 - \alpha) = \frac{v_{be}}{r_e} \left(1 - \frac{\beta}{\beta + 1}\right)$$

$$= \frac{v_{be}}{(\beta + 1)r_e} = \frac{v_{be}}{r_\pi}$$

If in the model of Fig (a) the current of the controlled source is expressed in terms of the emitter current as follows :

$$g_m v_{be} = g_m (i_e r_e)$$

$$= (g_m r_e) i_e =$$

We obtain alternative T-model shown in Fig (b). Here the BJT is represented as a current – controlled current source but with the control signal being i<sub>e</sub>.

αie

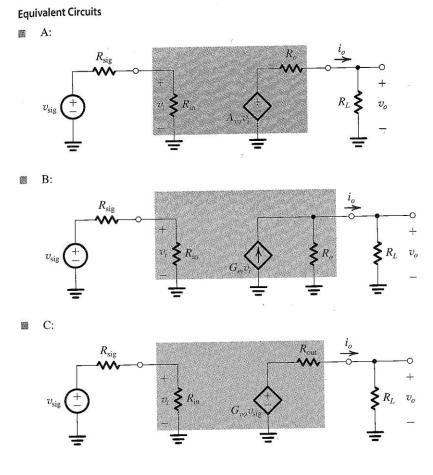

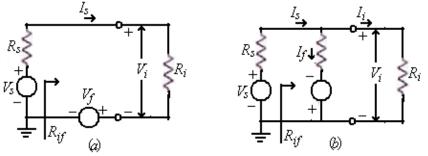

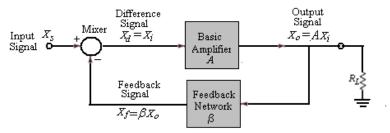

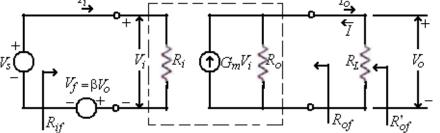

#### Circuit models for Amplifiers

Irrespective of complexity of the amplifier circuit, circuit can be represented as a building block in a system one must able to characterize, or model its terminal behaviour. In this section we will study simple but effective amplifier models.

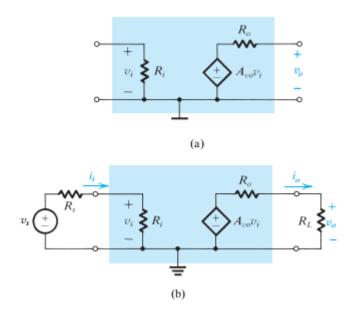

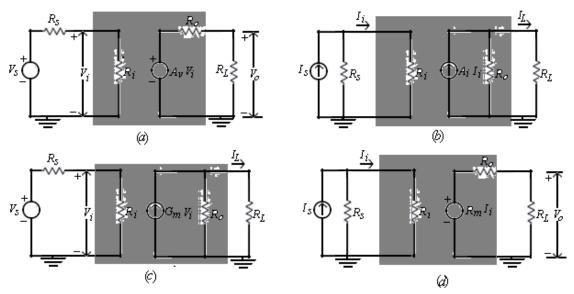

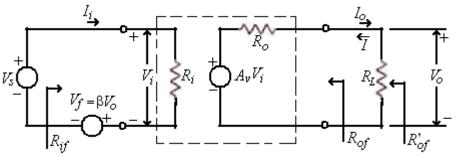

## **Voltage Amplifiers**

- > The model consists of Voltage controlled voltage source having a gain of factor of Avo

- An input resistance R<sub>i</sub> that accounts for amplifier draws an input current from the signal source.

- Output Resistance R<sub>o</sub> that accounts for the change in output voltage as the amplifier is called upon to supply output current to load.

# Fig.a) Circuit model for voltage amplifier, b) Voltage amplifier with input signal source and load

- A signal voltage source V<sub>s</sub> having a resistance R<sub>s</sub> connected to at the output to a load resistance R<sub>L</sub>.

- > The non-zero output resistance  $R_0$  causes only a fraction of  $A_{vo}V_i$  to appear across the output.

- Using voltage division rule we obtain

$$v_o = A_{vo}v_i \frac{R_L}{R_L + R_o}$$

Thus the voltage gain is given by

$$A_v \equiv \frac{v_o}{v_i} = A_{vo} \frac{R_L}{R_L + R_o}$$

> In order not to lose gain in coupling the amplifier output to load, the output resistance  $R_o$  should be much smaller than the load resistance  $R_L$  or to keep the output voltage  $v_o$  as constant as possible.

- An ideal voltage amplifier is one with R<sub>o</sub>=0,R<sub>L</sub>=∞,then A<sub>v</sub>=A<sub>vo</sub>. Where, A<sub>vo</sub>is the voltage gain of the unloaded amplifier, or open circuit voltage gain.

- The finite input resistance R<sub>i</sub> introduces another voltage divider action at the input, with the result that only a fraction of the source signal V<sub>s</sub> actually reaches the input terminals of the amplifier; that is

$$v_i = v_s \frac{R_i}{R_i + R_s}$$

> The overall voltage gain  $(V_o/V_s)$  can be found

$$\frac{v_o}{v_s} = A_{vo} \frac{R_i}{R_i + R_s} \frac{R_L}{R_L + R_o}$$

## **Cascaded Amplifiers**

To meet given amplifier specifications the need often arises to design the amplifier as a cascade of two or more stages. The stages are not usually identical. To illustrate the analysis and design of cascade amplifiers, we consider a practical example.

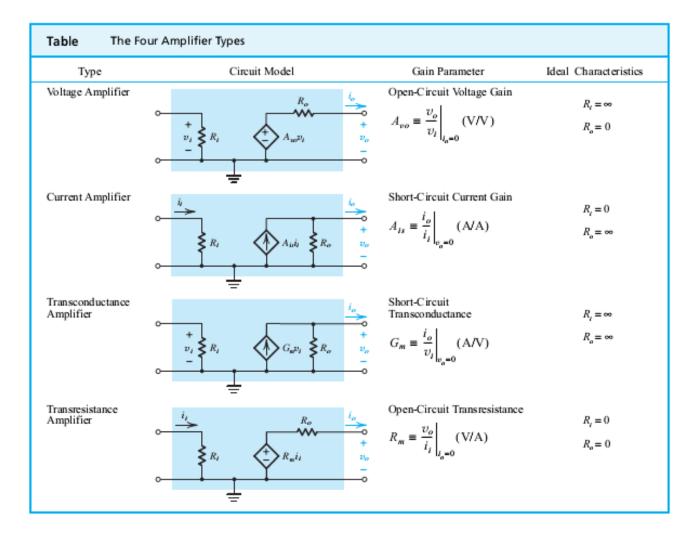

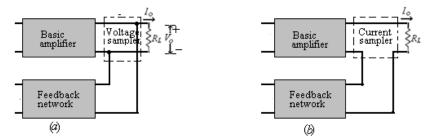

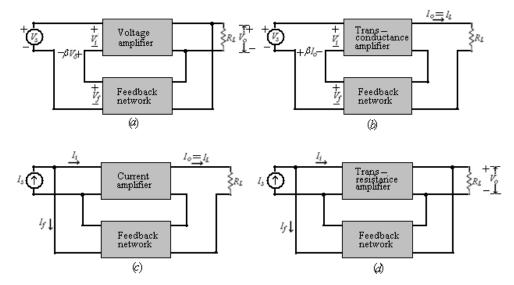

## **Other Amplifier Types**

The below table shows the four amplifier types, their circuit models ,the definition of their gain parameters, and the ideal values of their input and output resistances.

## **Frequency Response of Amplifiers**

An important characterization of an amplifier in terms of its response to input sinusoids of different frequencies. Such characterization of amplifier performance is known as the amplifier frequency response.

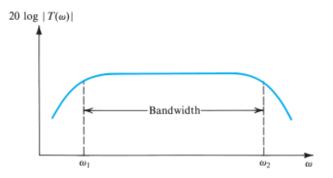

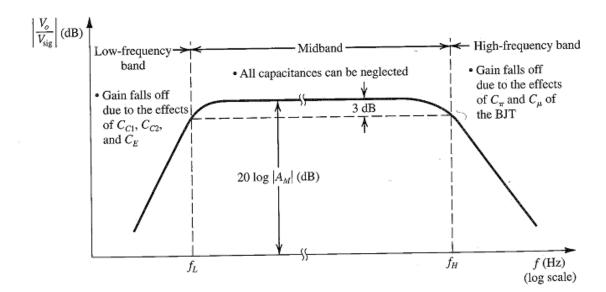

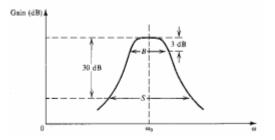

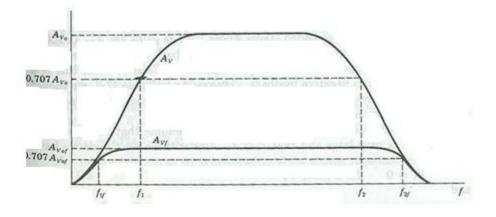

#### Amplifier bandwidth

The band of frequecies over which the gain of the amplifier is almost constant, to within a certain number of decibels(usually 3dB), is called the Amplifier bandwidth.

Fig. Typical magnitude response of amplifier.

# **SYLLABUS**

# 1.1 Low – frequency Single-stage MOS amplifiers

# **MOS** amplifiers

> In discrete circuits the MOSFET source is usually tied to the substrate, the body effect will be absent. Therefore we shall *not* take the body effect into account. Also, in some circuits we will neglect  $r_0$  in order to keep the analysis simple.

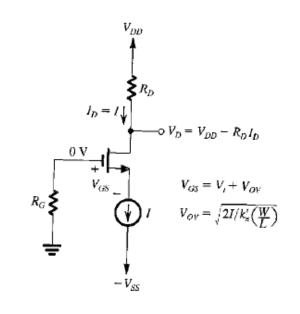

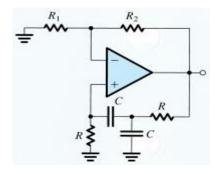

## **1.1.1 The Basic Structure**

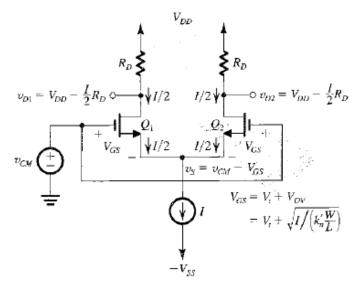

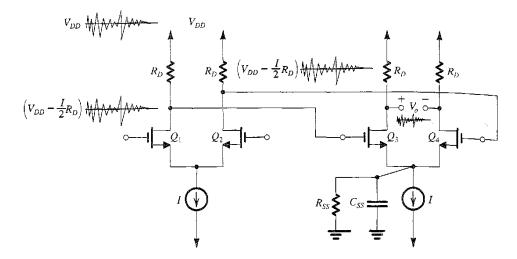

Figure 1.1 shows the basic circuit to implement the various configurations of discrete-circuit MOS amplifiers. Among the various schemes for biasing discrete MOS amplifiers, the constant-current biasing is employed for its effectiveness and simplicity. Figure 1.1 indicates the dc current and the dc voltages resulting at various nodes.

Fig.1.1: Basic structure of the circuit used to realize single-stage discrete-circuit MOS amplifier configurations.

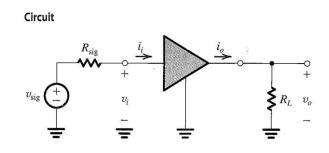

## **1.1.2 Characterizing Amplifiers**

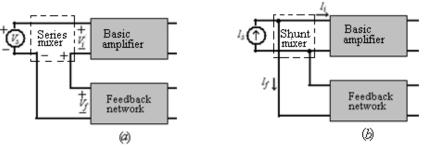

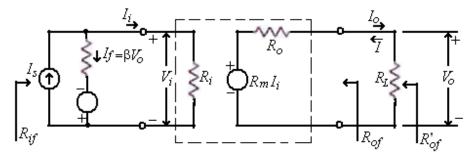

- Most of the amplifiers are non-unilateral amplifiers, i.e., they have internal feedback that may cause their input resistance to depend on the load resistance. Similarly, internal feedback may cause the output resistance to depend on the value of the resistance of the signal source feeding the amplifier. A number of remarks are in order:

- The amplifier is shown fed with a signal source having an open-circuit voltage v<sub>sig</sub> and an internal resistance R<sub>sig</sub>. These can be the parameters of an actual signal source or the Thevenin equivalent of the output circuit of another amplifier stage preceding the one under study in a cascade amplifier. Similarly, R<sub>L</sub> can be an actual load resistance or the input resistance of a succeeding amplifier stage in a cascade amplifier.

Parameters R<sub>t</sub>, R<sub>0</sub>, A<sub>v0</sub>, A<sub>is</sub>, and G<sub>m</sub> pertain to the amplifier proper; that is, they do not depend on the values of R<sub>sig</sub> and R<sub>L</sub>. By contrast, R<sub>in</sub>, R<sub>out</sub>, A<sub>v</sub>, A<sub>t</sub>, G<sub>v0</sub>, and G<sub>v</sub> may depend on one or both of R<sub>sig</sub> and R<sub>L</sub>. Also, observe the relationships of related pairs of these parameters; for instance,

$$R_i = R_{in}|_{R_{i,i}=\infty}$$

, and  $R_o = R_{out}|_{R_{i,i}=0}$ .

- For non-unilateral amplifiers,  $R_{in}$  may depend on  $R_L$ , and Rout may depend on  $R_{sig}$ . No such dependencies exist for unilateral amplifiers, for which  $R_{in} = R_i$  and Rout =  $R_0$ .

- The loading of the amplifier on the signal source is determined by the input resistance R<sub>in</sub>. The value of R<sub>in</sub> determines the current that the amplifier draws from the signal source. It also determines the proportion of the signal v<sub>sig</sub> that appears at the input of the amplifier proper (i.e., v<sub>t</sub>).

- When evaluating the gain Av from the open-circuit value A<sub>v0</sub>, R<sub>0</sub> is the output resistance. This is because Av is based on feeding the amplifier with an ideal voltage signal vt.

- > If the overall voltage gain  $G_v$  is to be calculated from its open-circuit value  $G_{v0}$ , the output resistance to use is Rout. This is because  $G_v$  is based on feeding the amplifier with vsig, which has an internal resistance Rsig.

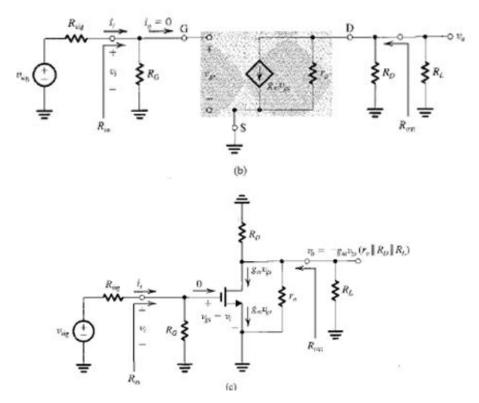

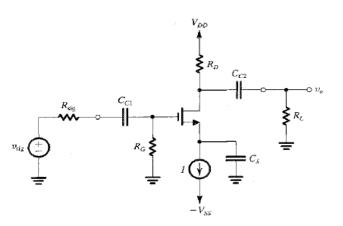

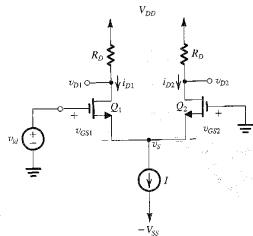

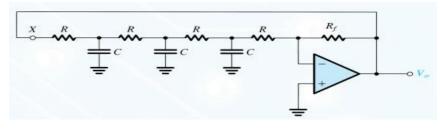

#### 1.1.3 Low – frequency response of the Common-Source (CS) Amplifier

- The common-source (CS) or grounded-source configuration is the most widely used of all MOSFET amplifier circuits. A common-source amplifier realized using the circuit of Fig. 1.1 is shown in Fig. 1.2 (a).

- Observe that to establish a signal ground, or an ac ground as it is sometimes called, at the source, we have connected a large capacitor, C<sub>s</sub>, between the source and ground. This capacitor, usually in the *pF* range, is required to provide a very small impedance (ideally, zero impedance; i.e., in effect, a short circuit) at all signal frequencies of interest.

- > In this way, the signal current passes through  $C_{s}$  to ground and thus *bypasses* the output resistance of current source *I*(and any other circuit component that might be connected to the MOSFET source); hence, *Cs* is called a **bypass capacitor.**

- > The lower the signal frequency, the less effective the bypass capacitor becomes. Here we shall assume that  $C_{s}$  is acting as a perfect short circuit and thus is establishing a zero signal voltage at the MOSFET source.

- > In order not to disturb the dc bias current and voltages, the signal to be amplified, shown as voltage source  $v_{sig}$  with an internal resistance  $R_{sig}$ , is connected to the gate through a large

capacitor  $C_{C1}$ . Capacitor  $C_{C1}$ , known as a **coupling capacitor**, is required to act as a perfect short circuit at all signal frequencies of interest while blocking dc.

- > As the signal frequency is lowered, the impedance of  $C_{C1}$  (i.e.,  $l/j\omega C_{C1}$ ) will increase and its effectiveness as a coupling capacitor will be correspondingly reduced.

- > Here we assume  $C_{Cl}$  is acting as a perfect short circuit as far as the signal is concerned. Before leaving  $C_{Cl}$ , where the signal source can provide an appropriate dc path to ground, the gate can be connected directly to the signal source and both  $R_G$  and  $C_{Cl}$  can be dispensed with.

- > The voltage signal resulting at the drain is coupled to the load resistance  $R_L$  via another coupling capacitor  $C_{C2}$ . We assume that  $C_{C2}$  acts as a perfect short circuit at all signal frequencies of interest and thus that the output voltage  $v_0 = v_d$ .

- > Note that  $R_L$  can be either an actual load resistor, to which the amplifier is required to provide its output voltage signal, or it can be the input resistance of another amplifier stage in cases where more than one stage of amplification is needed.

- To determine the terminal characteristics of the CS amplifier—that is, its input resistance, voltage gain, and output resistance—we replace the MOSFET with its small-signal model. The resulting circuit is shown in Fig. 1.2 (b).

- > This amplifier is unilateral. Therefore Rin does not depend on  $R_L$ , and thus  $R_{in} = R_i$ . Also, Rout will not depend on  $R_{sig}$ , and thus  $R_{out} = R_0$ . Analysis of this circuit is straight forward and proceeds in a step-by-step manner, from the signal source to the amplifier load. At the input

$$i_{g} = 0$$

$$R_{in} = R_{G}$$

$$v_{i} = v_{sig} \frac{R_{in}}{R_{in} + R_{sig}} = v_{sig} \frac{R_{G}}{R_{G} + R_{sig}}$$

$$v_{oo}$$

$$R_{in} = v_{ci} \frac{R_{in}}{R_{in} + R_{sig}} = v_{sig} \frac{R_{G}}{R_{G} + R_{sig}}$$

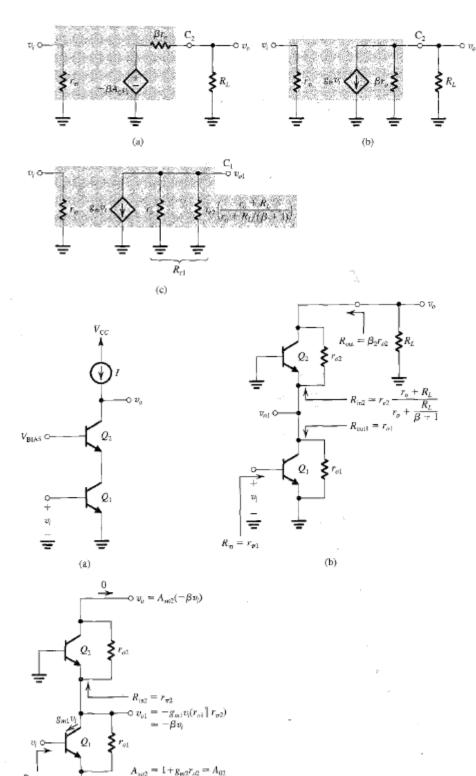

Fig. 1.2: (a) Common-source amplifier based on the circuit of Fig. 1.1, (b) Equivalent circuit of the amplifier for small-signal analysis, (c) Small-signal analysis performed directly on the amplifier circuit with the MOSFET model implicitly utilized.

> Usually  $R_G$  is selected very large (e.g., in the M $\Omega$  range) with the result that in many applications  $R_C >> R_{sig}$  and

$$v_i \equiv v_{sig}$$

$$v_{gs} = v_i$$

$$v_o = -g_m v_{gs} (r_o \parallel R_D \parallel R_f)$$

Thus the voltage gain  $A_{v}$  is

$$A_v = -g_m(r_o \parallel R_D \parallel R_L)$$

and the open-circuit voltage gain Avois

$$A_{oo} = -g_m(r_o \parallel R_D)$$

The overall voltage gain from the signal-source to the load will be

$$G_v = \frac{R_{\rm in}}{R_{\rm in} + R_{\rm sig}} A_v$$

$$= -\frac{R_G}{R_G + R_{\rm sig}} g_m(r_a \parallel R_D \parallel R_L)$$

Finally, to determine the amplifier output resistance  $R_{out}$  we set  $v_{sig}$  to 0; that is, we replace the signal generator  $v_{sig}$  with a short circuit and look back into the output terminal, as indicated in Fig. 1.2.

$$R_{out} = r_a \| R_D$$

- Including the output resistance v<sub>0</sub> in the analysis of the CS amplifier is straight forward: Since r<sub>0</sub> appears between drain and source, it in effect appears in parallel with R<sub>D</sub>. Since it is usually the case that r<sub>0</sub>>> R<sub>D</sub>, the effect of r<sub>0</sub> will be a slight decrease in the voltage gain and a decrease in Rout.

- Although small-signal equivalent circuit models provide a systematic process for the analysis of any amplifier circuit. Consider the Fig. 1.2 (c) the small-signal analysis of the CS amplifier performed on a somewhat simplified version of the circuit and its equivalent circuit is shown in Fig. 1.2 (b). The CS amplifier has a very high input resistance, a moderately high voltage gain, and a relatively high output resistance.

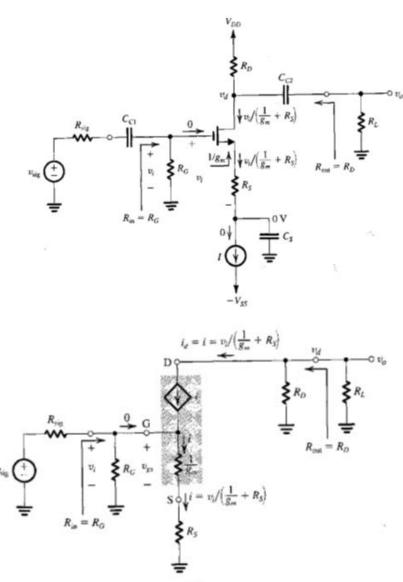

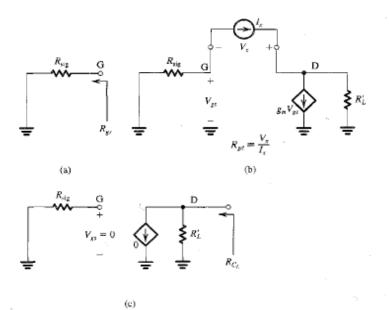

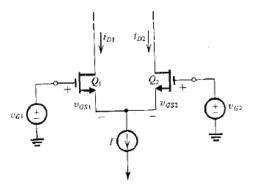

#### **1.1.4** The Common-Source Amplifier with a Source Resistance

- Here a resistance R<sub>s</sub> in the source lead of the common-source amplifier, as shown in Fig. 1.3 (a). The corresponding small-signal equivalent circuit is shown in Fig. 1.3 (b) where we note that the transistor has been replaced by its T equivalent-circuit model.

- The T model is used in preference to the  $\pi$  model because it makes the analysis simpler. In general, whenever a resistance is connected in the source lead, as for instance in the source-follower circuit, the T model is preferred: The source resistance then simply appears in series with the resistance 1/g<sub>m</sub> which represents the resistance between source and gate, looking into the source.

- > We have not included  $r_0$  in the equivalent-circuit model. Including  $r_0$  would complicate the analysis considerably;  $r_0$  would connect the output node of the amplifier to the input side and thus would make the amplifier non-unilateral.

- From Fig. 1.3 (b) we see that as in the case of the CS amplifier,

$$v_i = v_{sig} \frac{R_G}{R_G + R_{sig}}$$

$R_{\rm in} = R_{\rm c} = R_{\rm cl}$

Unlike the CS circuit, however, here v<sub>gs</sub> is only a fraction of v<sub>I</sub>. It can be determined from the voltage divider composed of l/g<sub>m</sub> and R<sub>S</sub> that appears across the amplifier input as follows:

$$v_{gs} = v_i \frac{\frac{1}{g_m}}{\frac{1}{g_m} + R_s} = \frac{v_i}{1 + g_m R_s}$$

- > Thus we can use the value of  $R_s$  to control the magnitude of the signal  $v_{gs}$  and thus ensure that  $v_{gs}$  does not become too large and cause unacceptably high nonlinear distortion. This is the first benefit of including resistor  $R_s$ .

- R<sub>S</sub> causes the useful bandwidth of the amplifier to be extended. The mechanism by which Rs causes such improvement in amplifier performance is that of negative feedback. The current i<sub>d</sub> is equal to the current i flowing in the source lead; thus,

$$i_d = i = \frac{v_i}{\frac{1}{g_m} + R_s} = \frac{g_m v_i}{1 + g_m R_s}$$

# Fig. 1.3: (a) Common-source amplifier with a resistance Rs in the source lead, (b) Small-signal equivalent circuit with r<sub>0</sub> neglected.

- Thus including  $R_S$  reduces  $i_d$  by the factor  $(1 + g_m R_S)$ , since this is the factor relating  $v_{gs}$  to  $v_i$  and the MOSFET produces  $i_d = g_m v_{gs}$ . The above drain current equation indicates also that the effect of RS can be thought of as reducing the effective  $g_m$  by the factor  $(1 + g_m R_S)$ .

- > The output voltage can now be found from

$$v_o = -i_d(R_D \parallel R_L)$$

$$= -\frac{g_m(R_D \parallel R_L)}{1 + g_m R_S} v_i$$

Thus the voltage gain is

$$A_v = -\frac{g_m(R_D \parallel R_L)}{1 + g_m R_S}$$

And setting  $R_L = \infty$  gives

$$A_{vo} = -\frac{g_m R_D}{1 + g_m R_S}$$

$\succ$  The overall voltage gain G<sub>0</sub> is

$$G_{v} = -\frac{R_{G}}{R_{G} + R_{sig}} \frac{g_{m}(R_{D} \parallel R_{L})}{1 + g_{m}R_{S}}$$

- > Comparing the above three equations, with their counterparts without  $R_s$  indicates that including  $R_s$  results in a gain reduction by the factor (1 +  $g_m R_s$ ). This factor is called the amount of feedback and that it determines both the magnitude of performance improvements and, the reduction in gain.

- A resistance R<sub>S</sub> in the source lead increases dc bias stability; that is, R<sub>S</sub> reduces the variability in I<sub>D</sub>. The action of R<sub>S</sub> that reduces the variability of I<sub>D</sub>.Rs in the circuit of Fig. 1.3 is reducing id. Because of its action in reducing the gain, R<sub>S</sub> is called source degeneration resistance.

- Another useful interpretation of the voltage gain expression is that the gain from gate to drain is simply the ratio of the total resistance in the drain, (R<sub>D</sub> in parallel with R<sub>L</sub>), to the total resistance in the source, [(l/g<sub>m</sub>) + Rs].

# **1.2 BJT Amplifiers**

- > There are three basic configurations for single-stage BJT amplifiers:

- Common-Emitter

- Common-Base

- Common-Collector

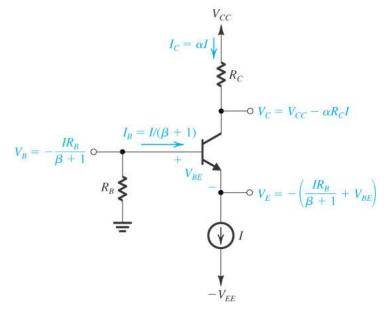

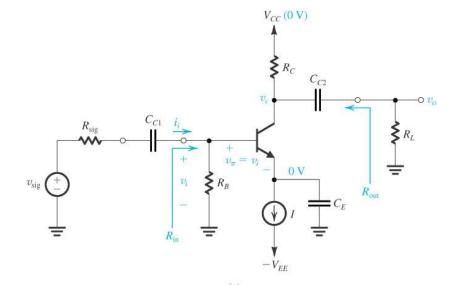

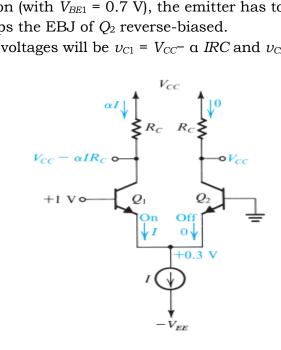

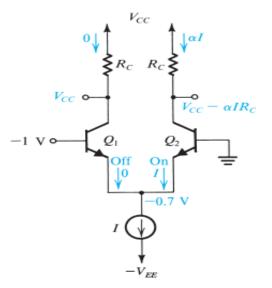

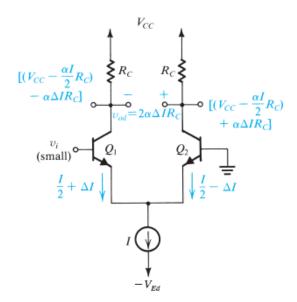

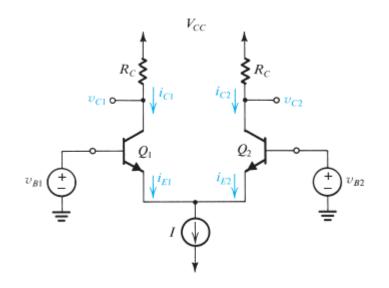

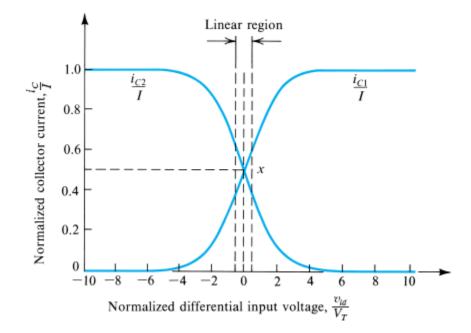

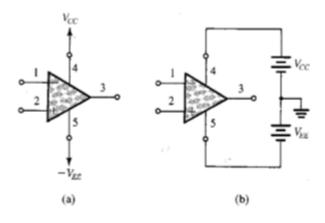

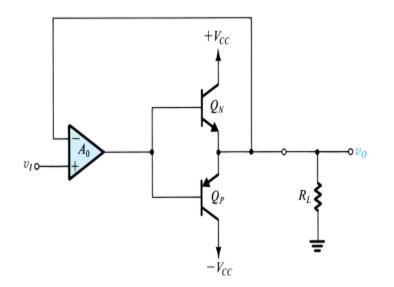

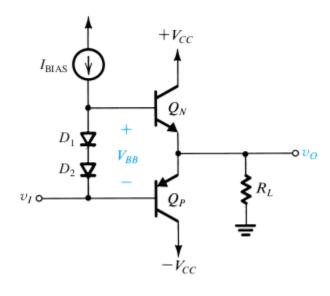

#### 1.2.1 The basic structure of BJT amplifier

> The basic circuit that utilize to implement the various configurations of BJT amplifiers with constant current biasing is shown in figure 1.4. The value of  $R_B$  is selected as large value in order to keep the input resistance at the base large. However it is also required to limit the dc voltage drop across  $R_B$

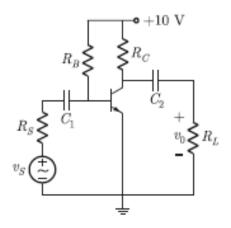

Fig. 1.4: Basic structure of the circuit used to realize single-stage, discrete-circuit BJT amplifier configurations

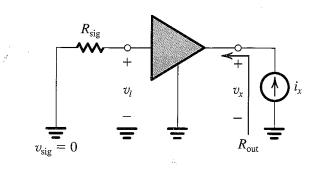

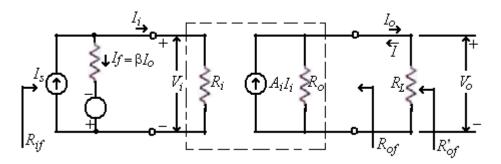

#### **1.2.2** Characterizing BJT amplifiers

To use BJT amplifier circuits, it is important to know how to characterize the performance of amplifiers as circuit building blocks. These amplifiers have internal feedback that may cause their input resistance to depend on the load resistance. Similarly internal feedback may cause the output resistance to depend on the value of the resistance of the signal source feeding the amplifier.

#### Definitions

Input resistance with no load:

$$R_i \equiv \left. \frac{v_i}{i_i} \right|_{R_L = \infty}$$

Input resistance:

$$R_{\rm in} \equiv \frac{v_i}{i_i}$$

Open-circuit voltage gain:

$$A_{vo} \equiv \left. \frac{v_o}{v_i} \right|_{R_L = \infty}$$

Woltage gain:

$$A_v \equiv \frac{v_o}{v_i}$$

Short-circuit current gain:

$$A_{is} \equiv \frac{i_o}{i_i} \bigg|_{R_L = 0}$$

Current gain:

$$A_i \equiv \frac{i_o}{i_i}$$

Short-circuit transconductance:

$$G_m \equiv \left. \frac{i_o}{v_i} \right|_{R_L = 0}$$

Output resistance of amplifier proper:

$$R_o \equiv \frac{v_x}{i_x} \bigg|_{v_i=0}$$

Output resistance:

$$R_{\rm out} \equiv \left. \frac{v_x}{i_x} \right|_{v_{\rm sig}=0}$$

ς.,

Open-circuit overall voltage gain:

$$G_{vo} \equiv \left. \frac{v_o}{v_{\rm sig}} \right|_{R_L^{=\infty}}$$

Overall voltage gain:

$$G_v \equiv \frac{v_o}{v_{\rm sig}}$$

Relationships

$$\frac{v_i}{v_{\text{sig}}} = \frac{R_{\text{in}}}{R_{\text{in}} + R_{\text{sig}}} \qquad \qquad G_v = \frac{R_{\text{in}}}{R_{\text{in}} + R_{\text{sig}}} A_{vo} \frac{R_L}{R_L + R_o}$$

$$A_v = A_{vo} \frac{R_L}{R_L + R_o} \qquad \qquad G_{vo} = \frac{R_i}{R_i + R_{\text{sig}}} A_{vo}$$

$$A_{vo} = G_m R_o \qquad \qquad G_v = G_{vo} \frac{R_L}{R_L + R_{\text{out}}}$$

- 1. The amplifier should fed with a signal source having an open circuit voltage  $v_{sig}$  and an internal resistance  $R_{sig}$ . These can be the parameters of an actual signal source or the Thevenin equivalent of the output circuit of another amplifier stage in a cascade amplifier stage. Similarly,  $R_L$  be the actual load resistance or the input resistance of a succeeding stage in a cascading amplifier.

- Parameters R<sub>i</sub>, R<sub>o</sub>, A<sub>vo</sub>, A<sub>is</sub> and G<sub>m</sub> pertain to the amplifier proper; i.e., they do not depend on the values of R<sub>sig</sub> and R<sub>L</sub>. R<sub>in</sub>, R<sub>out</sub>, A<sub>v</sub>, A<sub>i</sub>, G<sub>vo</sub> and G<sub>v</sub> may depend on the values of R<sub>sig</sub> and R<sub>L</sub>. Relationships of related pairs: R<sub>i</sub> = R<sub>in</sub>|R<sub>L</sub>=∞ and R<sub>o</sub>= R<sub>out</sub>|R<sub>sig</sub>=0

- 3. For non-unilateral amplifiers,  $R_{in}$  may depends on  $R_L$  and  $R_{out}$  depends on  $R_{sig}$ . No such dependencies exists for unilateral amplifiers, for which  $R_{in} = R_i$  and  $R_{out} = R_o$

- 4. The *loading* of the amplifier on the signal source is determined by the input resistance  $R_{in}$ . The value of  $R_{in}$  determines the current that the amplifier draws from the signal source. It also determines the proportion of the signal  $v_{sig}$  that appears at the input of the amplifier proper, that is,  $v_i$ .

- 5. When evaluating the gain Av from the open-circuit value  $A_{vo}$ ,  $R_0$  is the output resistance to use. This is because A,, is based on feeding the amplifier with an ideal voltage signal  $v_i$ .

On the other hand, if we are evaluating the overall voltage gain  $G_v$  from its open-circuit value  $G_{v0}$  the output resistance to use is  $R_{out}$ . This is because  $G_v$  is based on feeding the amplifier with  $v_{sig}$ , which has an internal resistance  $v_{sig}$ .

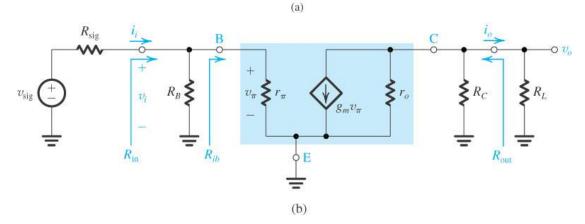

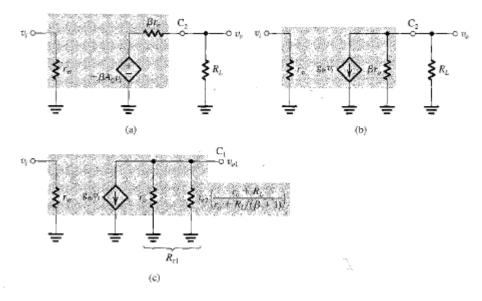

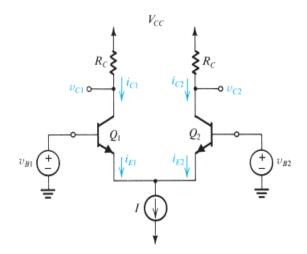

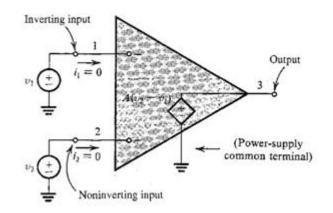

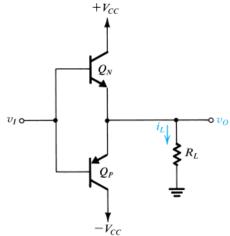

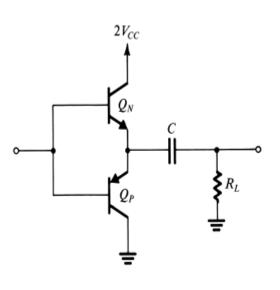

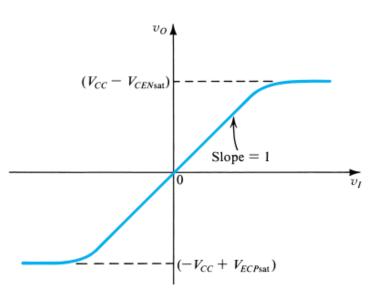

#### 1.2.3 Low – frequency response of the Common-Emitter Amplifier

- First, assume Re=0 (this is not re, but an explicit resistor)

- The BJT is biased with a current source (with high output impedance) and a capacitor connects the emitter to ground.Capacitor provides an AC short at the emitter for small time-varying signals but is an open circuit for DC signals

- $\blacktriangleright$  Can redraw the circuit with an equivalent circuit that replaces the BJT with its hybrid- $\pi$  model

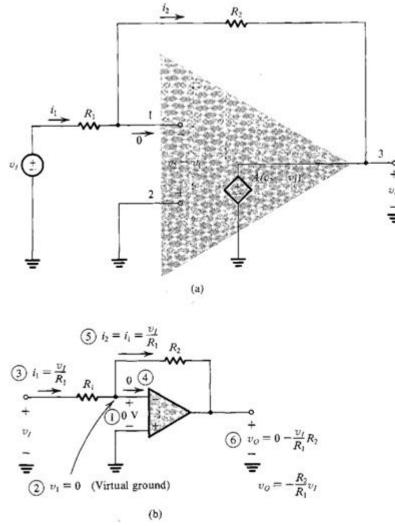

Fig. 1.5: a) CE Amplifier, b) Equivalent circuit by replacing BJT with  $\pi$ -model

> The terminal characteristics of amplifier are analysed as

$$R_{\rm in} \equiv \frac{v_i}{i_i} = R_B \parallel R_{ib}$$

where  $R_{ib}$  is the input resistance looking into the base. Since the emitter is grounded,

$$R_{ib} = r_{\pi}$$

Normally we select  $R_B >> r_{\pi}$ , which results  $R_{in} \equiv r_{\pi}$

The fraction of source signal will appear across the input terminals of the amplifier and is given by,

$$v_{i} = v_{sig} \frac{R_{in}}{R_{in} + R_{sig}}$$

$$= v_{sig} \frac{(R_{B} \parallel r_{\pi})}{(R_{B} + r_{\pi}) + R_{sig}}$$

$v_i \cong v_{\rm sig} \frac{r_{\pi}}{r_{\pi} + R_{\rm sig}}$

$v_{\pi} = v_i$

which for  $R_B \ge r_{\pi}$  becomes

Next we note that

At the output of the amplifier we have

$$v_o = -g_m v_\pi (r_o \parallel R_C \parallel R_L)$$

> The voltage gain of the amplifier is

$$A_v = -g_m(r_o \parallel R_C \parallel R_L)$$

> The open circuit voltage gain is obtained by making  $R_L = \infty$

$$A_{vo} = -g_m(r_o \parallel R_C)$$

from which we can say that the effect of  $r_0$  is simply to reduce the gain, usually  $r_0 >> R_C$ , results in

$$A_{vo} \cong -g_m R_C$$

The output resistnace  $R_{out}$  can be found from the equivalent circuit 1.5 (b) by looking back into the output terminal while short-circuiting the source  $v_{sig}$ . This will result in  $v_{\pi} = 0$ , and

$$R_{\text{out}} = R_C \parallel r_o$$

Thus  $r_0$  reduces the output resistance of the amplifier, typically  $r_0 >> R_C$  and

$$R_{\text{out}} \cong R_C$$

For this unilateral amplifier  $R_0 = R_{out}$ , we can use  $A_{v0}$  and  $R_0$  to obtain the voltage gain  $A_v$  corresponding to any particular  $R_L$ ,

$$A_v = A_{vo} \frac{R_L}{R_L + R_o}$$

The overall voltage gain from source to load,  $G_{\nu}$  can be obtained by multiplying  $(v_i/v_{sig})$  by  $A_{\nu}$ ,

$$G_{v} = -\frac{(R_{B} || r_{\pi})}{(R_{B} || r_{\pi}) + R_{\text{sig}}} g_{m}(r_{o} || R_{C} || R_{L})$$

For the case  $R_B >> r_{\pi}$ , this expression simplifies to

$$G_v \cong -\frac{\beta(R_C \parallel R_L \parallel r_o)}{r_\pi + R_{\rm sig}}$$

And voltage gain reduces to

$$G_v \cong -g_m(R_C \parallel R_L \parallel r_o)$$

> The short circuit current gain is calculated as

$$i_{os} = -g_m v_\pi$$

Since  $v_{\pi}$  is related to  $i_i$ by

$$v_{\pi} = v_i = i_i R_{in}$$

The short-circuit current gain can be found as

$$A_{is} \equiv \frac{i_{os}}{i_i} = -g_m R_{in}$$

Substituting  $R_{in} = R_B \| r_{\pi}$ , we can see that in the case  $R_B >> r_{\pi}$ ,  $|A_{is}|$  reduces to  $\beta$ , which is to be expected since  $\beta$  is the short – circuit current gain of the common – emitter configuration.

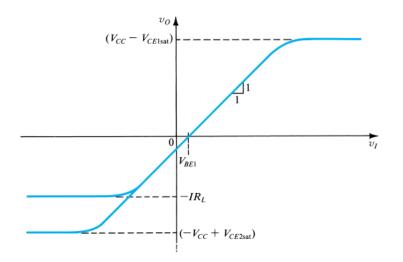

**Conclusion:**the common emitter configuration can provide large voltage gain, large current gain, low input resistance and relatively high output resistance.

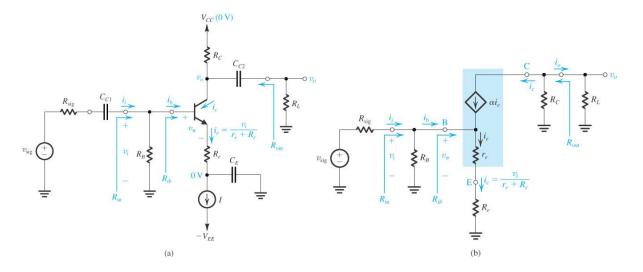

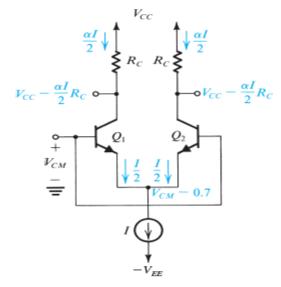

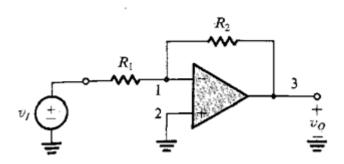

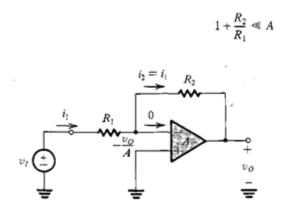

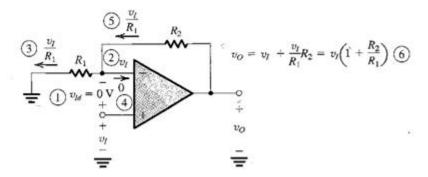

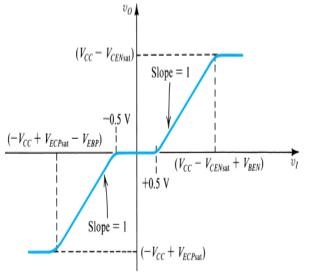

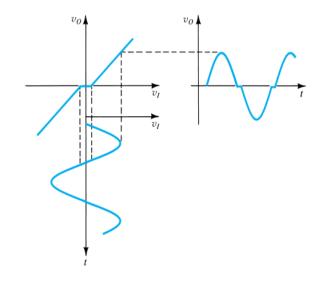

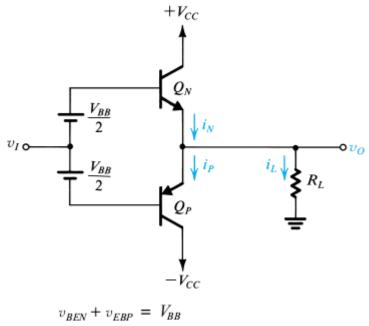

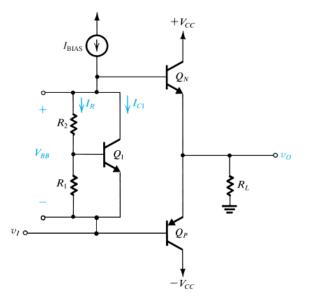

#### 1.2.4 Common Emitter Amplifier with Emitter Resistance

Characteristics with Re

- gain is less with but less dependent on β

- input resistance is higher

- allows higher input signal voltage

Fig. 1.6: a) CE Amplifier with emitter resistor, b) Equivalent circuit by replacing BJT with Tmodel

T determine the amplifier input resistance  $R_{in}$ , form the equivalent circuit shown in figure 1.6 (b), at the input  $R_{in}$  is the parallel equivalent of  $R_B$  and the input resistance at the base  $R_{ib}$ .

$$R_{\rm in} = R_B \parallel R_{ib}$$

The input resistance at the base  $R_{ib}$  can be found from

where

$i_b = (1 - \alpha)i_e = \frac{i_e}{\beta + 1}$

$R_{ib} \equiv \frac{v_i}{i_b}$

and

$i_e = \frac{v_i}{r_e + R_e}$

Thus,

$$R_{ib} = (\beta + 1)(r_e + R_e)$$

It says that the input resistance looking into the base is  $(1+\beta)$  times the total resistance in the emitter. Multiplication by the factor  $(1+\beta)$  is known as resistance – reflection rule.

$$\frac{R_{ib} \text{ (with } R_e \text{ included)}}{R_{ib} \text{ (without } R_e)} = \frac{(\beta+1)(r_e + R_e)}{(\beta+1)r_e}$$

$$= 1 + \frac{R_e}{r_e} \cong 1 + g_m R_e$$

To determine the voltage gain  $A_{\nu}$ ,

$$v_o = -i_c(R_C \parallel R_L)$$

$$= -\alpha i_e(R_C \parallel R_L)$$

$A_v \equiv \frac{v_o}{v_i} = -\frac{\alpha(R_C \parallel R_L)}{r_e + R_e}$

Since

$$\alpha \cong 1$$

,

$$A_v \cong -\frac{R_C \parallel R_L}{r_e + R_e}$$

The open circuit voltage gain is given by

$$A_{vo} = -\frac{\alpha R_C}{r_e + R_e}$$

which can be expressed alternatively as

$$A_{vo} = -\frac{\alpha}{r_e} \frac{R_C}{1 + R_e/r_e}$$

$$A_{vo} = -\frac{g_m R_C}{1 + (R_e/r_e)} \cong -\frac{g_m R_C}{1 + g_m R_e}$$

Including  $R_e$  thus reduces the voltage gain by the factor  $(1+g_mR_e)$ , which is the same factor by which  $R_{ib}$  is increased.

The output resistance  $R_{out}$  can be found from the circuit,  $R_{out} = R_C$ .

The short – circuit current gain  $A_{is}$  can be found from the circuit

$$i_{os} = -\alpha i_e$$

$i_i = v_i / R_{in}$

$$A_{is} = -\frac{\alpha R_{in} i_e}{v_i}$$

$$A_{is} = -\frac{\alpha(R_B \parallel R_{ib})}{r_e + R_e}$$

which for the case  $R_B \ge R_{ib}$  reduces to

$$A_{is} = \frac{-\alpha(\beta+1)(r_e + R_e)}{r_e + R_e} = -\beta$$

the same value as for the CE circuit.

The overall voltage gain from source to load can be obtained by multiplying  $A_v$  by  $(v_i/v_{sig})$

$$G_v = \frac{v_i}{v_{\text{sig}}} \cdot A_v = -\frac{R_{\text{in}}}{R_{\text{sig}} + R_{\text{in}}} \frac{\alpha(R_C \parallel R_L)}{r_e + R_e}$$

Substituting for  $R_{in}$  by  $R_B \parallel R_{ib}$ , assuming that  $R_B \gg R_{ib}$ , and substituting for  $R_{ib}$

$$G_v \cong -\frac{\beta(R_C \parallel R_L)}{R_{\text{sig}} + (\beta + 1)(r_e + R_e)}$$

This gain is lower than that of the CE amplifier because of the additional term  $(1+\beta)$  R<sub>e</sub> in the denominator.

$$\frac{v_{\pi}}{v_i} = \frac{r_e}{r_e + R_e} \cong \frac{1}{1 + g_m R_e}$$

Thus, for the same  $v_{\pi}$ , the signal at the input terminal of the amplifier,  $v_i$ , can be greater than for the CE amplifier by the factor (1+g<sub>m</sub>R<sub>e</sub>).

## **Conclusion:**

- The input resistance  $R_{ib}$  is increased by the factor  $(1+g_mR_e)$ .

- The voltage gain from base to collector,  $A_v$  is reduced by the factor  $(1+g_mR_e)$ .

- For the same nonlinear distortion, the input signal  $v_i$  can be increased by the factor  $(1+g_mR_e)$ .

- The overall voltage gain is less dependent on the value of  $\beta$ .

- The high frequency response is significantly improved.

| UNII-I                                                                       |                                              |  |  |  |

|------------------------------------------------------------------------------|----------------------------------------------|--|--|--|

| Assignment-Cum-Tutorial Questions                                            |                                              |  |  |  |

| A. Objective Questions                                                       |                                              |  |  |  |

| 1. Which of the following is true in case of                                 | f unilateral amplifiers [ ]                  |  |  |  |

| a) Input resistance doesn't depend or                                        | ı R <sub>L</sub>                             |  |  |  |

| b) Output resistance doesn't depend                                          | on R <sub>sig</sub>                          |  |  |  |

| c) Both a & b                                                                |                                              |  |  |  |

| d) None of the above.                                                        |                                              |  |  |  |

| 2. All practical amplifiers are                                              | [ ]                                          |  |  |  |

| a) Unilateral                                                                | b) Non-unilateral                            |  |  |  |

| c) May be sometimes unilateral                                               | d)None                                       |  |  |  |

| 3. The phase difference between the out                                      | put and input voltages of a CE amplifier is  |  |  |  |

|                                                                              | [ ]                                          |  |  |  |

| a) 180° b) 0° c) 90                                                          | o d) 270º                                    |  |  |  |

| 4. The purpose of capacitors in a transis                                    | tor amplifier is to [ ]                      |  |  |  |

| a) Protect the transistor                                                    | b) Cool the transistor                       |  |  |  |

| b) Couple or bypass a.c. component                                           | d)Provide biasing                            |  |  |  |

| 5. If the input capacitor of a transistor amplifier is short-circuited, then |                                              |  |  |  |

| a) Transistor will be destroyed                                              | [ ]<br>b) Biasing conditions will change     |  |  |  |

| c)Signal will not reach the base                                             | d) None of the above                         |  |  |  |

| <ul><li>6. The amplifier works as a linear system</li></ul>                  |                                              |  |  |  |

| a) High frequency signals                                                    | b) Low frequency signals                     |  |  |  |

|                                                                              |                                              |  |  |  |

| c)Small signals                                                              | d) large signals                             |  |  |  |

| 7. State the differences between Unilatera                                   | al and Non Unilateral Amplifiers             |  |  |  |

| 8. Draw the CS Amplifier and its equivale                                    | nt circuit for small- signal analysis.       |  |  |  |

| 9. Draw the CS Amplifier with source                                         | resistance and its equivalent circuit for    |  |  |  |

| small- signal analysis                                                       |                                              |  |  |  |

| 10. Why Source Resistance in CS amp                                          | lifier also called as "Source degeneration"  |  |  |  |

| resistance.                                                                  |                                              |  |  |  |

| 11. Define Bandwidth and Figure of Me                                        | _                                            |  |  |  |

| 12. Draw the basic structure of the ci                                       | rcuit used to realize single-stage discrete- |  |  |  |

UNIT-I

- 12. Draw the basic structure of the circuit used to realize single-stage discretecircuit BJT amplifier configurations.

- 13. Draw the frequency response curve of an amplifier?

14. Draw the basic structure of the circuit used to realize single-stage discretecircuit MOS amplifier configurations.

## **B.Subjective Questions**

- 1. What are the characteristic parameters of amplifiers? Define & provide relationships.

- Explain the Small signal operation of CS amplifier. Find the expressions for input resistance (R<sub>in</sub>), Output resistance (R<sub>out</sub>), voltage gain (A<sub>v</sub>) and overall voltage gain(G<sub>v</sub>).

- 3. Analyse the CS amplifier with source degeneration resistance to find the expressions for  $R_{in}$ ,  $R_{out}$ ,  $A_v$  and  $G_v$ .

- 4. Analyse the CE amplifier with emitter degeneration resistance to find the expressions for  $R_{in}$ , Rout,  $A_v$ ,  $i_{os}$  and  $G_v$ .

- 5. Explain the small signal operation of CE amplifier & deduce the expressions for  $R_{in}$ ,  $R_{out}$ ,  $A_v$ ,  $i_{os}$  and  $G_v$ .

- 6. Considering a CS amplifier, find  $R_{in}$ ,  $A_{vo}$ , and  $R_{out}$ , both without and with  $r_o$  taken into account. Then calculate the overall voltage gain  $G_v$ , with  $r_o$  taken into account, for the case  $R_{sig} = 100 \text{ k}\Omega$ ,  $R_L = 15 \text{ k}\Omega$ . If  $v_{sig}$  is a 0.4V Peak to peak sinusoid, what output signal  $v_o$  results?

- 7. Calculate the overall voltage gain  $G_v$  of a common source amplifier for which  $g_m = 2 \text{ mA/V}$ ,  $r_0 = 50 \text{ k}\Omega$ ,  $R_D = 10 \text{ K}\Omega$ , and  $R_G = 10 \text{ M}\Omega$ . The amplifier is fed from a signal source with a Thevenin resistance of 0.5 M $\Omega$ , and the amplifier output is coupled to a load resistance of 20 K $\Omega$ .

- 8. A CS amplifier using an NMOS transistor biased in the manner as shown in below figure for which  $g_m = 2 \text{ mA/V}$  is found to have an overall voltage gain  $G_0$  of -16 V/V. What value should a resistance  $R_S$  inserted in the source lead have to reduce the voltage gain by a factor of 4?

9. The overall voltage gain of the amplifier as shown in below figure was measured with a resistance  $R_s$  of 1 K $\Omega$  in place and found to be -10 V/V. When  $R_s$  is shorted, but the circuit operation remained linear the gain doubled. What must  $g_m$  be? What value of  $R_s$  is needed to obtain an overall voltage gain of-8V/V?

- 10. A BJT amplifier is measured to have  $R_i = 10 \text{ k}\Omega$ .  $A_{v0} = 100 \text{ V/V}$ , and  $R_0 = 100 \Omega$ . Also, when a load resistance  $R_L$  of 1 k $\Omega$  is connected between the output terminals, the input resistance is found to decrease to 8 k $\Omega$ . If the amplifier is fedwith a signal source having an internal resistance of 2 k $\Omega$ , find  $G_m$ ,  $A_v$ ,  $G_{v0}$ ,  $G_v$ ,  $R_{out}$ , and  $A_i$ .

- 11. In the circuit shown below,  $v_{sig}$  is a small sinewave signal with zero average. The transistor  $\beta$  is 100.

- (a) Find the value of  $R_E$  to establish a dc emitter current of about 0.5 mA.

- (b) Find  $R_C$  to establish a dc collector voltage of about +5 V.

- (c) For  $R_L = 10 \ k\Omega$  and the transistor  $r_0 = 200 \ k\Omega$ , draw the small-signal equivalent circuit of the amplifier and determineits overall voltage gain.

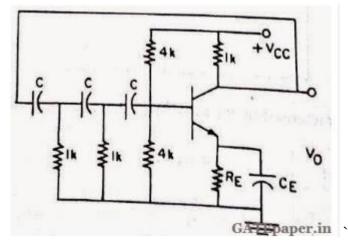

# **C. GATE questions**

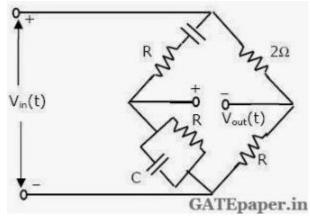

1. A small signal source  $V_i$  (t) = (Acos 20t +Bsin 10 t) is applied to a transistor amplifieras shown below. The transistorhas  $\beta$  = 150 and  $h_{ie}$ = 3 $\Omega$ . Which expression bestapproximate  $V_0(t)$ ? (GATE 2009) [ ]

- (A)  $V_0(t) = 1500(A\cos 20t + B\sin 10 t)$

- (B)  $V_0(t) = 1500(A\cos 20t + B\sin 10 t)$

- (C)  $V_0(t) = 1500Bsin 10 t$

- (D)  $V_0(t)$ = 150Bsin 10 t

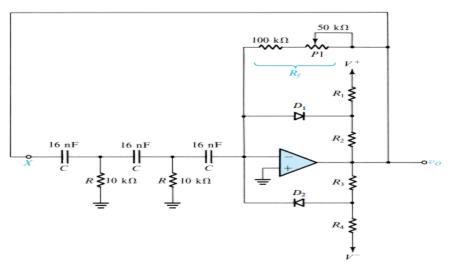

- The amplifier circuit shown below uses a silicon transistor. The capacitors Cc and CE can be assumed to be short at signal frequency and effect of output Resistancer₀ can be ignored. If CE is disconnected from the circuit, which one of the followingstatements is true? (GATE 2010) [ ]

- (A) The input resistance  $R_i$  increases and magnitude of voltage gain  $A_V$  decreases

- (B) The input resistance  $R_i$  decreases and magnitude of voltage gain  $A_V$  increases

- (C) Both input resistance  $R_i$  and magnitude of voltage gain  $A_V$  decreases

- (D) Both input resistance  $R_i$  and the magnitude of voltage gain  $A_V$  increases

- 3. Consider the common emitter amplifier shown below with the following circuit

parameters:

$\beta$ =100, $g_m$ =0.3861A/V, $r_0$ =259 $\Omega$ , $R_s$ =1k $\Omega$ , $R_B$ =93k $\Omega$ , $R_c$ =250k $\Omega$ , $R_L$ =1k $\Omega$ , $C_1$ =3 $\mu$ Fand $C_2$ = 4.7  $\mu$ F

| The resistance seen by the source $v_S$ is(GATE 2010) |            |           |       | [ | ] |

|-------------------------------------------------------|------------|-----------|-------|---|---|

| (A) 258 Ω                                             | (B) 1258 Ω | (C) 93 kΩ | (D) ∞ |   |   |

# Unit – II

## High – frequency single – stage amplifiers

# **Objectives**

- To Discuss the General considerations of High frequency Response of an amplifier.

- To Discuss the High-frequency response of the CS and CE amplifiers

- Analysis CS and CE of amplifiers using Miller's theorem

- To analyze, and characterize the different Cascode Amplifiers like MOS Cascode and BJT Cascode

- To analyze, and characterize the Darlington configuration.

# **Syllabus**

General considerations, high-frequency response of CS and CE amplifiers, cascade amplifier, Darlington configuration.

# **Pre-requisites**

- The MOSFET internal Capacitances

- The High-Frequency MOSFET Model

- The BJT Internal Capacitances and High Frequency Model

- Circuit models for amplifiers

- The terms: Frequency response and Bandwidth of an amplifier

# **Outcomes:**

Students will be able to

Draw, analyse, and characterize the MOS and BJT single-stage amplifiers at high frequencies.

Draw, analyze, and characterize - Cascode, Darlington,

# **Pre-requisites**

# THE MOSFET INTERNAL CAPACITANCES :

There are basically two types of internal capacitances in the MOSFET

**1. The gate capacitive effect:** The gate electrode (polysilicon) forms a parallel-plate capacitor with the channel, with the oxide layer serving as the capacitor dielectric. W e discussed the gate (or oxide) capacitance in previous sections and denoted its value per unit area as *Cox*.

**2. The source-body and drain-body depletion-layer capacitances:** These are the capacitances of the reverse-biased pn junctions formed by the n+ source region (also called the diffusion) and the p-type substrate and by the n+ drain region (the drain diffusion) and the substrate.

## The Junction Capacitances :

The depletion-layer capacitances of the two reverse-biased junctions formed between each of the source and the drain diffusions and the body can b e determined using the formula developed in previous Section . Thus, for the source diffusion, we have the source body capacitance, Csb,

$$C_{sb} = \frac{C_{sb0}}{\sqrt{1 + \frac{V_{SB}}{V_0}}}$$

here  $Csb_0$  is the value of Csb at zero body-source bias, VSB is the magnitude of the reverse bias voltage, and  $V_0$  is the junction built-in voltage (0.6V to 0.8V). Similarly, for the drain diffusion, we have the drain-body capacitance Cdb,

$$C_{db} = \frac{C_{db0}}{\sqrt{1 + \frac{V_{DB}}{V_0}}}$$

## The High-Frequency MOSFET Model:

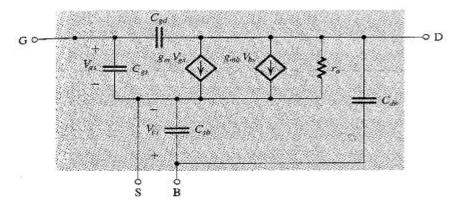

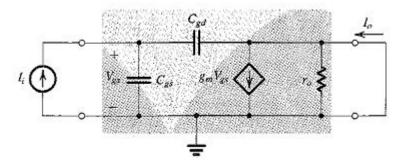

The below figure shows the high frequency model of MOSFET by adding all the capacitances.

Figure 1a: High-frequency equivalent circuit model for the MOSFET.

Figure 1b: The equivalent circuit for the case in which the source is connected to the substrate (body),

Figure 1c: The equivalent circuit model of (b) with *Cdb* neglected (to simplify analysis).

The MOSFET Unity-Gain Frequency (*f*<sub>T</sub>):

Figure 2: Circuit for determining the short-circuit current gain  $I_0/I_1$ .

A figure of merit for the high-frequency operation of the MOSFET as an amplifier is the unity-gain frequency,  $f_T$ . This is defined as the frequency at which the short-circuit current gain of the common-source configuration becomes unity. The above figure shows the MOSFET hybrid  $\Pi$ - model with the source as the common terminal between the input and output ports. To determine the short-circuit current gain, the input is fed with a current-source signal  $I_i^{\bullet}$  and the output terminals are short-circuited. It is easy to see that the current in the short circuit is given by

$$I_o = g_m V_{gs} - s C_{gd} V_{gs}$$

let us assume Cgd is a very small value and it can be neglected

w e can express Vgs in terms of the input current  $I_i$  as

$$V_{gs} = I_i / s(C_{gs} + C_{gd})$$

By the above two equations we can get the short circuit current gain as

$$\frac{I_o}{I_i} = \frac{g_m}{s(C_{gs} + C_{gd})}$$

For physical frequencies S=JW, it can be seen that the magnitude of the current gain becomes unity at the frequency

$$\omega_T = g_m / (C_{gg} + C_{gd})$$

Thus the unity-gain frequency  $f_{\rm T}$  is given as

$$\hat{f}_T = \frac{g_m}{2\pi (C_{gs} + C_{gd})}$$

Hence  $f_{\rm T}$  is proportional to gm and inversely proportional to the FET internal capacitances.

#### The BJT Internal Capacitances and High Frequency Model

The high frequency response of BJT amplifiers rolls off due to short circuiting effect of internal capacitances. These internal capacitances are resulting from charge- storage effects.

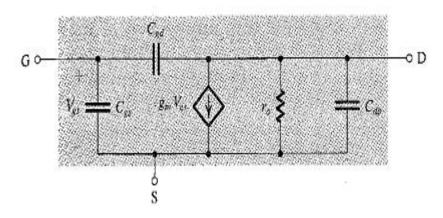

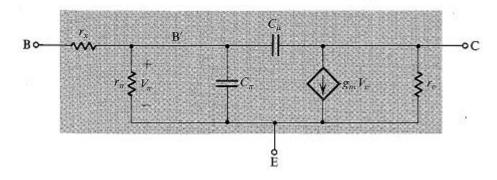

The High frequency Hybrid-  $\pi$  model is shown as below.

Fig. The High- Frequency Hybrid -  $\pi$  model

r<sub>x</sub> : Base Spreading Resistance :

It is the resistance between the external base terminal B and internal node B' (also called as implicit node, bulk node). Its typical value is  $100\Omega$ . negligible at low frequencies but effective at high frequencies.

$r_{\Pi}$ : It is the resistnace looking into the base terminal.

typical value is  $1K\Omega$ .

There are two sources of internal capacitances effect

- 1. Base- Emitter Capacitance  $C\pi$

- 2. Collector Base Junction Capacitance Cµ

#### **1.** Base- Emitter Capacitance Cπ :

$C\pi$  is the sum of two capacitances .Cde Emitter- Base Diffusion Capacitance

Cje Emitter – Base Junction Capacitance.

$$C\pi = Cde + Cje$$

i) Cde Emitter- Base Diffusion Capacitance: It is called as Base – Charging or Diffusion Capacitance Cde.

It is due to minority carrier storage in the base region when the transistor is operating in the active or satuaration mode. i.e when Emitter- Base Junction (EBJ) is forward biased.

$Cde = dQ/dv_{BE}$

considering, an npn transistor in active region..

$$i_C = I_S e^{v_{BE}/V_T} \tag{1}$$

$$I_{S} = \frac{A_{E}qD_{n}n_{i}^{2}}{N_{A}W}$$

(2)

$$Q_{n} = \frac{A_{E}qWn_{i}^{2}}{2N_{A}}e^{v_{BE}/V_{T}}$$

(3)

Using 1, 2, 3

$$Q_n = \frac{W^2}{2D_n}i_C = \tau_F i_C$$

where,

$$\tau_F = \frac{W^2}{2D_n}$$

$\tau_F$  is known as the forward base- transit time. It represents the average time a charge carrier (electron) spends in crossing the base.

$$C_{de} \equiv \frac{dQ_n}{dv_{BE}}$$

$$= \tau_F \frac{di_C}{dv_{BE}}$$

$$C_{de} = \tau_F g_m = \tau_F \frac{I_C}{V_T}$$

# ii :Cje :: Base – Emitter Junction Capacitance

$$C_{je} = \frac{C_{je0}}{\left(1 - \frac{V_{BE}}{V_{0e}}\right)^m}$$

Where, Cje0 is the value of Cjeat VBE = 0V.

$V_{0e}$  is the EBJ built in voltage (0.7 – 0.9 V)

$m = grading \ coefficient$ , typically 1/2.

For a forward biased EBJ in the active mode, Cje = 2 Cje0

Typical value of  $C\pi$  is 100pF.

#### 2. The Collector – Base Junction Capacitance Cµ

This is the capacitance of the reverse biased Collector – Base Junction (CBJ) .

$$C_{\mu} = \frac{C_{\mu 0}}{\left(1 + \frac{V_{CB}}{V_{0c}}\right)^m}$$

where  $C\mu 0$  is the value of  $C\mu$  at VCB = 0V.

Voc is the CBJ built in voltage (typically 0.75 V)

m is grading coefficient = 1/2 to 1/3.

Typical value of  $C\mu = 3pF$ .

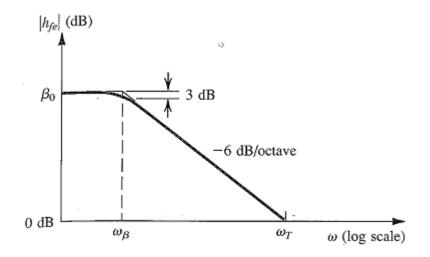

## Unity Gain Frequency (F<sub>T</sub>)

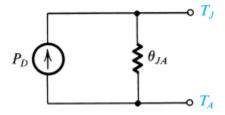

Fig. The Circuit for deriving an expression for Short Circuit current gain  $h_{fe}(s) = Ic/Ib$ .

$$I_c = (g_m - sC_\mu)V_\pi \qquad (1)$$

$$h_{fe} \equiv \frac{I_c}{I_b} = \frac{g_m - sC_\mu}{1/r_\pi + s(C_\pi + C_\mu)}$$

(3)

Since,

$$g_m \gg \omega C_\mu;$$

$$h_{fe} \simeq \frac{g_m r_\pi}{1 + s(C_\pi + C_\mu) r_\pi}$$

$$h_{fe} = \frac{\beta_0}{1 + s(C_\pi + C_\mu)r_\pi}$$

Where  $\beta_0$  is the low frequency value of  $\beta$

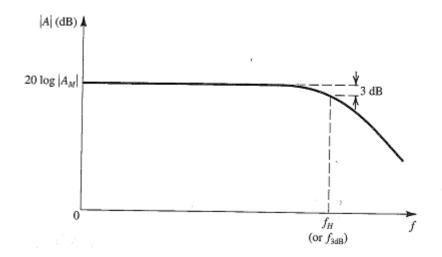

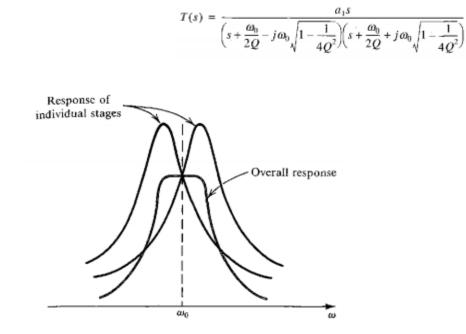

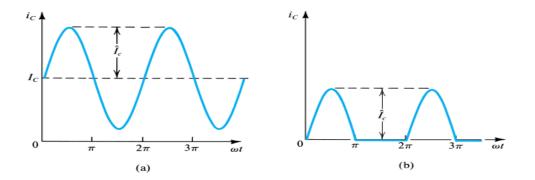

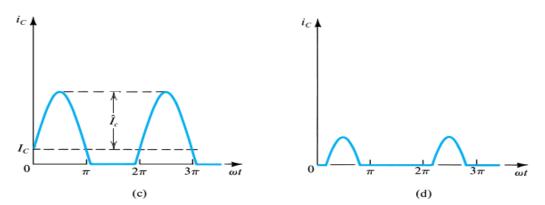

Fig. Frequency Response of h<sub>fe</sub>

$f_{\beta}$  is the 3-dB frequency

$$\omega_{\beta} = \frac{1}{(C_{\pi} + C_{\mu})r_{\pi}}$$

$\omega_T = \beta_0 \omega_\beta$

Thus

$$\omega_T = \frac{g_m^2}{C_\pi + C_\mu}$$

$$f_T = \frac{g_m}{2\pi(C_\pi + C_\mu)}$$

Frequency Response of CE Amplifier:

**Low frequency Band**: The gain roll off in this region is due to coupling and bypass capacitors acting as open circuit & internal capacitances are open and in significant.

**Mid frequency Band:** In this region coupling and bypass capacitors will be short circuited; where as the internal capacitances are open circuits and still in effective. Hence the gain is maximum and almost constant.

**High frequency Band:** The gain roll off in this region is due to internal capacitances getting slowly short circuiting.

# **SYLLABUS**

**2.1 High Frequency Response** – General Consideration, The high-frequency gain function, Determining the 3-dB frequency  $f_{H}$ , Using open-circuit time constants for the approximate determination of  $f_{H}$ ,

### 2.1.1 General Consideration

The various stages in an integrated- circuit cascade amplifier are directly coupled; that is they do not utilize coupling capacitors. Hence the mid band gain remains constant down to zero frequency.

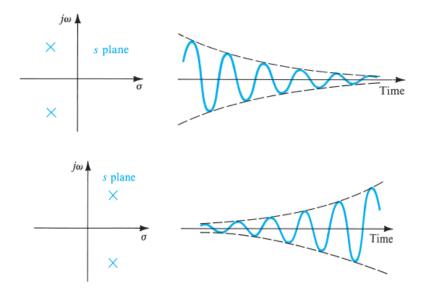

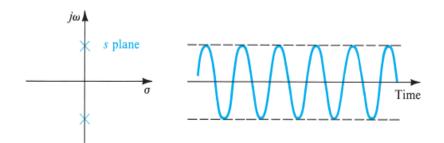

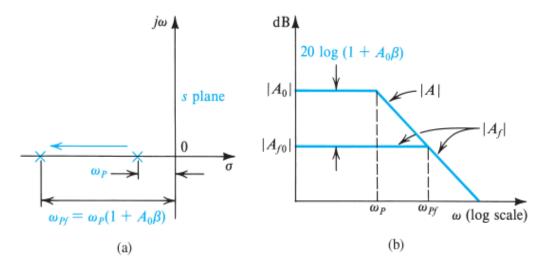

#### 2.1.2 The High- Frequency Gain Function:

The amplifier gain, taking into account the internal transistor capacitances, can be expressed as a function of the complex frequency variable s in the general form

$$A(s) = A_M F_H(S)$$

where  $A_M$  is the midband gain.

Considering the generalized transfer function

$$F_{H}(s) = \frac{(1 + s/\omega_{Z1})(1 + s/\omega_{Z2})\dots(1 + s/\omega_{Zn})}{(1 + s/\omega_{P1})(1 + s/\omega_{P2})\dots(1 + s/\omega_{Pn})}$$

where wp1, wp2, .... wpn are pole frequencies.

wz1, wz2,.... 2zn are zero frequencies.

#### 2.1.3 Determining the 3-dB frequency f<sub>H</sub>:

i) Dominant pole is present:

The amplifier designer usually is particularly interested in the part of the high-frequencyband that is close to the midband. This is because the designer needs to estimate-and ifneed be modify-the value of the upper 3-dB frequency  $f_{\rm H}$ . In many cases the zeros are either at infinity or suchhigh frequencies as to be of little significance to the determination of a)H.

If in addition one of the poles, says  $w_{Pl}$ , is of much lower frequency than any of the other poles, then this polewill have the greatest effect on the value of the amplifier  $w_{H}$ . In other words, this pole willdominate the high-frequency response of the amplifier, and the amplifier is said to have **adominant-pole response**. In such cases the function  $F_{H}(s)$  can be approximated by

$$F_H(s) \cong \frac{1}{1 + s/\omega_{P_1}}$$

If a dominant pole exists, then the determination of  $W_{\rm H}$  is greatly simplified

$$\omega_{\!_H} \cong \omega_{P1}$$

This approximation is valid only when the **Dominant pole** is existing.

A **Dominant pole** is said to be existing iff the lowest frequency pole is at least two octaves (a factor of 4) lowest from nearest pole or zero.

ii) Dominant pole not existing

If a dominant pole does not exist, the 3-dB frequency  $W_H$  can be determined alternatively, by an approximate formula for  $w_H$ , that can be derived as follows:

Consider, for simplicity, the case of a circuit having two poles and two zeros in the high-frequency

Band; that is

$$F_{H}(s) = \frac{(1 + s/\omega_{Z1})(1 + \bar{s}/\omega_{Z2})}{(1 + s/\omega_{P1})(1 + s/\omega_{P2})}$$

Substituting  $s = j\omega$  and taking the squared magnitude gives

$$|F_H(j\omega)|^2 = \frac{(1+\omega^2/\omega_{Z1}^2)(1+\omega^2/\omega_{Z2}^2)}{(1+\omega^2/\omega_{P1}^2)(1+\omega^2/\omega_{P2}^2)}$$

By definition, at  $\omega = \omega_H$ ,  $|F_H|^2 = \frac{1}{2}$ ; thus,

$$\frac{1}{2} = \frac{(1 + \omega_H^2 / \omega_{Z1}^2)(1 + \omega_H^2 / \omega_{Z2}^2)}{(1 + \omega_H^2 / \omega_{P1}^2)(1 + \omega_H^2 / \omega_{P2}^2)}$$

$$= \frac{1 + \omega_H^2 \left(\frac{1}{\omega_{Z1}^2} + \frac{1}{\omega_{Z2}^2}\right) + \omega_H^4 / \omega_{Z1}^2 \omega_{Z2}^2}{1 + \omega_H^2 \left(\frac{1}{\omega_{P1}^2} + \frac{1}{\omega_{P2}^2}\right) + \omega_H^4 / \omega_{P1}^2 \omega_{P2}^2}$$

Since  $w_H$  is usually smaller than the frequencies of all the poles and zeros, So by neglecting the terms containing fourth order  $w_H$  terms.

$$\omega_H \cong 1 / \sqrt{\frac{1}{\omega_{P1}^2} + \frac{1}{\omega_{P2}^2} - \frac{2}{\omega_{Z1}^2} - \frac{2}{\omega_{Z2}^2}}$$

This relationship can be extended to any number of poles and zeros as

$$\omega_H \cong 1 / \sqrt{\left(\frac{1}{\omega_{P_1}^2} + \frac{1}{\omega_{P_2}^2} + \cdots\right) - 2\left(\frac{1}{\omega_{Z_1}^2} + \frac{1}{\omega_{Z_2}^2} + \cdots\right)}$$

## iii) Using Open Circuit Time Constants for the Approximate Determination of f<sub>H</sub>

it is not a simple matter determine the poles and zeros by quick hand analysis. In such cases an approximate value for  $f_H$  can be obtained using this method.

Considering the generalized transfer function

$$F_H(s) = \frac{(1 + s/\omega_{Z1})(1 + s/\omega_{Z2})\dots(1 + s/\omega_{Zn})}{(1 + s/\omega_{P1})(1 + s/\omega_{P2})\dots(1 + s/\omega_{Pn})}$$

$$F_H(s) = \frac{1 + a_1 s + a_2 s^2 + \dots + a_n s^n}{1 + b_1 s + b_2 s^2 + \dots + b_n s^n}$$

where the coefficients a and b are related to the frequencies of the zeros and poles, respec-tively. Specifically, the coefficient b1 is given by

$$b_1 = \frac{1}{\omega_{p_1}} + \frac{1}{\omega_{p_2}} + \dots + \frac{1}{\omega_{p_n}}$$

.....(1)

The value of **b1** can be obtained by considering the various capacitances in the high-frequency equivalent circuit one at a time whilereducing all other capacitors to zero (or, equivalently, replacing them with open circuits). That is, to obtain the contribution of capacitance C, we reduce all other capacitances to zero, reduce input signal source to zero and determine the resistance Rio seen by Ci.

This process is repeated for all other capacitors in the circuit. The value of b1 is computed by summing the individual time constants, hence called Open – Circuit Time Constants.

$$b_1 = \sum_{i=1}^{n} C_i R_{io}$$

Now the approximate value of f<sub>H</sub>can be obtained by considering there exist a dominant pole w<sub>P1</sub> then

from eq.(1)

$$b_1 \simeq \frac{1}{\omega_{p_1}}$$

But also upper 3dB frequency will be approximately equal to w<sub>p1</sub>leading to the approximation

$$\omega_H \simeq \frac{1}{b_1} = \frac{1}{\left[\sum\limits_i C_i R_{io}\right]}$$

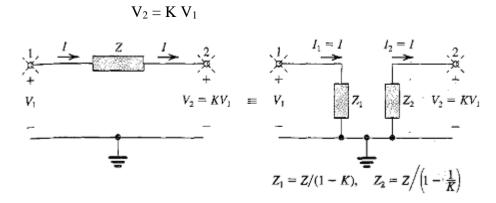

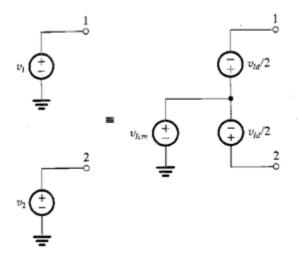

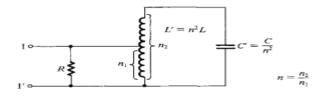

### **2.2 MILLERS THEORM:**

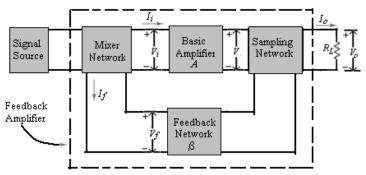

Consider the situation in Figure 5a As a part of a larger circuit that is not shown, we have isolated two circuit nodes, labeled 1 and 2, between which an impedance Z is connected. Nodes 1 and 2 are also connected to other parts of the circuit, as signified by the broken lines emanating from the two nodes. Furthermore, it is assumed that somehow it has been determined that the node voltage at node 2 is related to the node 1 by

The Miller equivalent circuit.

In typical situations K is a gain factor that can be positive or negative and that has a magnitude usually larger than unity. This, however, is not an assumption for Miller's theorem. Miller's theorem states that impedance Z can be replaced by two impedances: Z1 connected between node 1 and ground and Z2 connected between node 2 and ground, where

$$Z_1 = Z/(1-K)$$

and

$$Z_2 = Z \left/ \left( 1 - \frac{1}{K} \right) \right.$$

The current entering in to node1 is given as below

$$I_1 = \frac{V_1}{Z_1} = I = \left(\frac{V_1 - KV_1}{Z}\right)$$

similarly current entering into node2 is given as below

$$I_2 = \frac{0 - V_2}{Z_2} = \frac{0 - KV_1}{Z_2} = I = \frac{V_1 - KV_1}{Z}$$

Although not highlighted, the Miller equivalent circuit derived above is valid only as long as the rest of the circuit remains unchanged; otherwise the ratio of ,V2 to V1 might change. It follows that the Miller equivalent circuit cannot be used directly to determine the output resistance of an amplifier. This is because in determining output resistances it is implicitly assumed that the source signal is reduced to zero and that a test-signal source (voltage or current) is applied to the output terminals—obviously a major change in the circuit, rendering the Miller equivalent circuit no longer valid.

**2.3 High-frequency response of the CS and CE amplifiers** : High-frequency response of the CS and CE amplifiers, Analysis using Miller's theorem, Analysis using open-circuit time constants, Exact analysis, Adapting the formulas for the case of the CE amplifier, The situation when  $R_{sig}$  is low

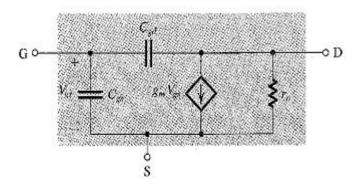

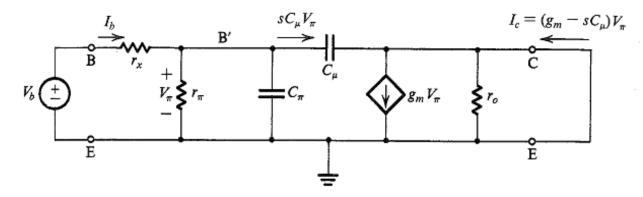

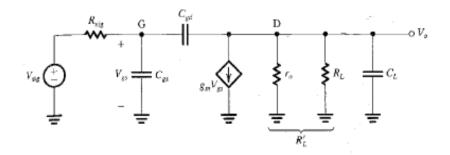

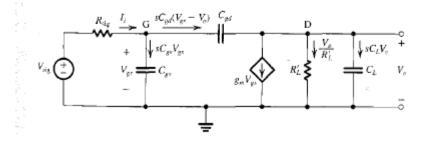

# 2.3 High-frequency response of the CS and CE amplifiers:

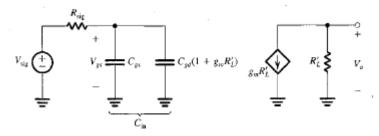

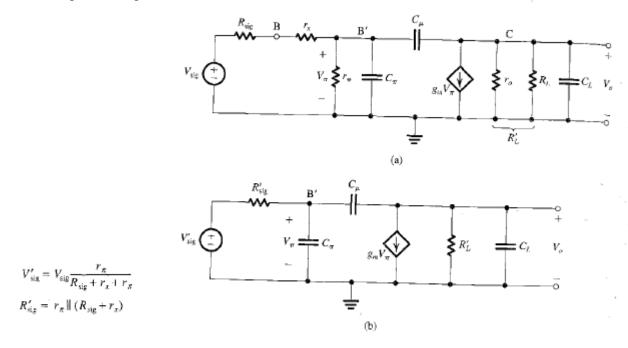

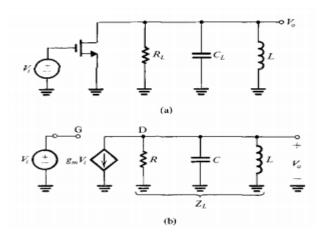

The above figure shows the High-frequency response equivalent circuit of the common source amplifier. This equivalent circuit applies equally well to the CE amplifier while a simple relabeling of components Cgs would be replaced by  $C_{II}$ , Cgd by Cµ and obviously Vgs by  $v_{II}$ .

The input-signal source is represented by Vsig and *Rsig*. In some cases, however, Vsig and *Rsig* would be modified values of the signal-source voltage and internal resistance, taking into account other resistive components such as a bias resistor  $R_G$  or  $R_B$ , the BJT resistances rx and  $r\pi$ , etc. The load

resistance RL represents the combination of an actual load resistance (if one is connected) and the output resistance of the current-source load. To avoid loss of gain,  $R_L$  is usually on the same order as  $r_0$ . We combine  $R_L$  with  $r_a$  and denote their parallel equivalent  $R_L$ '. The load capacitance  $C_L$  represents the total capacitance between drain (or collector) and ground; it includes the drain-to-body capacitance Cdb (collector-to-substrate capacitance), the input capacitance of a succeeding amplifier stage, and in some cases, as we shall see in later chapters, a deliberately introduced capacitance. In IC MOS amplifiers,  $C_L$  can be relatively substantial.

## 2.3.1 Analysis Using Miller's Theorem

In situations when Rsig is relatively large and  $C_L$  is relatively small, Miller's theorem can be used to obtain a quick but approximate estimate of the 3-dB frequency  $f_H$ . Below fig shows the approximate equivalent circuit obtained for the CS case, from which we see that the amplifier has a dominant pole formed

by  $R_{vig}$  and  $C_{in}$ . Thus,

where

$$\frac{v_o}{V_{\text{sig}}} \cong \frac{XM}{1 + \frac{S}{\omega_H}}$$

.4

U

$$A_M = -g_m R_L'$$

and the 3-dB frequency  $f_H = \omega_H / 2\pi$  is given by

$$f_B = \frac{1}{2\pi C_{in}R_{sig}}$$

where

$$C_{in} = C_{gd} + C_{gd}(1 + g_m R_{l_i}^{\prime})$$

## 2.3.2 Analysis Using Open-Circuit Time Constants

The method of open-circuit time constants can b e directly applied to the CS equivalent circuit of from which we see that the resistance seen by Cgs, Rgs = Rsig and that seen by  $C_L$  is  $R'_L$ . The resistance R d seen by Cgd can b e found by analyzing the circuit.

Thus the effective time-constant  $b_1$  or  $t_H$  can be found as

$$\begin{aligned} \tau_{H} &= C_{gs} R_{gs} + C_{gd} R_{gd} + C_{L} R_{C_{L}} \\ &= C_{gs} R_{sig} + C_{gd} [R_{sig} (1 + g_{w} R_{L}') + R_{L}'] + C_{L} R_{L}' \end{aligned}$$

and the 3-dB frequency  $f_H$  is

$f_H \equiv \frac{1}{2\pi\tau_H}$

# 2.3.3 Exact Analysis

The approximate analysis presented above provides insight regarding the mechanism by which and the extent to which the various capacitances limit the high-frequency gain of t he CS (and CE) amplifiers. A node equation at the drain provides

$$sC_{gd}(V_{gs} - V_{u}) = g_{m}V_{gs} + \frac{V_{p}}{R_{L}^{\prime}} + sC_{L}V_{o}$$

which can be manipulated to the form

$$V_{gs} = \frac{-V_{o}}{g_{m}R'_{L}} \frac{1 + s(C_{L} + C_{gd})R'_{L}}{1 - sC_{gd}/g_{m}}$$

A loop equation at the input yields

$$V_{sig} = I_i R_{sig} + V_{gg}$$

in which we can substitute for  $I_i$  from a node equation at G,

$$I_i = sC_{gs}V_{gs} + sC_{gd}(V_{gs} - V_o)$$

to obtain

$$V_{sig} = V_{gs} [1 + s(C_{gs} + C_{gd})R_{sig}] - sC_{gd}R_{sig}V_{d}$$

We can now substitute in this equation for  $V_{gr}$  from Eq. (6.59) to obtain an equation in  $V_{sig}$  and  $V_{sig}$  that can be arranged to yield the amplifier gain as

$$\frac{V_{c}}{V_{sig}} = \frac{-(g_{si}R_L')[1 - s(C_{gd}/g_m)]}{1 + s\{[C_{gs} + C_{gd}(1 + g_mR_L')]R_{sig} + (C_L + C_{gd})R_L'\} + s^2[(C_L + C_{gd})C_{gs} + C_LC_{gd}]R_{sig}R_L'\}}$$

The above transfer function indicates that the amplifier has a second-order denominator, and hence two poles. Now, since the numerator is of the first order, it follows that one of the two transmission zeros is at infinite frequency. This is readily verifiable by noting that as *s* approaches  $\infty$ , (*V0* / Vsig ) approaches zero. The second zero is at

$$s = s_Z = \frac{g_m}{C_{gd}}$$

That is, it is on the positive *real axis* of the s-plane and has a frequency  $\omega_z$ ,

$$\omega_z = g_m / C_{ga}$$

Since *gm* is usually large and  $C_{gd}$  is usually small,  $f_z$  is normally a very high frequency and thus has negligible effect on the value of  $f_H$ .

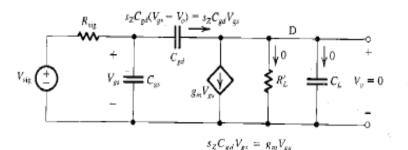

It is useful at this point to show a simple method for finding the value of *s* at which Vo = 0—that is, *sz*. Below Figure shows the circuit at s = sz. By definition,  $V_0 = 0$  and a node equation at D yields

Now, since  $V_{gr}$  is not zero (why not?), we can divide both sides by  $V_{gr}$  to obtain

$$s_Z = \frac{g_m}{C_{gd}}$$

Before considering the poles, we should note that as *s* goes toward zero, K/Vsig approaches the dc gain ( $-g_m R'_L$ ), as should be the case. Let's now take a closer look at the denominator polynomial. First, we observe that the coefficient of the *s* term is equal to the effective time-constant  $\tau_H$  obtained using the open-circuit time-constants method. Again, this should have been expected since it is the basis for the open-circuit time-constants method. Next, denoting the frequencies of the two poles  $\omega_{p1}$  and  $\omega_{p2}$ , we can express the denominator polynomial D(s) as

$$D(s) = \left(1 + \frac{s}{\omega_{p_1}}\right) \left(1 + \frac{s}{\omega_{p_2}}\right)$$

$$= 1 + s \left(\frac{1}{\omega_{p_1}} + \frac{1}{\omega_{p_2}}\right) + \frac{s^2}{\omega_{p_1}\omega_{p_2}}$$

Now, if  $\omega_{p1} >> \omega_{p2}$ —that is, the pole at  $\omega_{p1}$  is dominant—we can approximate D(s) as

$$D(s) \cong 1 + \frac{s}{\omega_{P1}} + \frac{s^2}{\omega_{P1}\omega_{P2}}$$

Equating the coefficients of the s term in denominator polynomial

$$\begin{split} \omega_{P1} &\cong \frac{1}{[C_{gr} + C_{gd}(1 + g_m R_L')]R_{iig} + (C_L + C_{gd})R_L'} \\ \omega_{P2} &= \frac{[C_{gr} + C_{gd}(1 + g_m R_L')]R_{iig} + (C_L + C_{gd})R_L'}{[(C_L + C_{gd})C_{gs} + C_L C_{gd}]R_L'R_{iig}} \end{split}$$

# 2.3.4 Adapting the Formulas for the Case of the CE Amplifier

Adapting the formulas presented above to the case of the CE amplifier is straightforward. First, note from how Vsig and Rsigs are modified to take into account the effect of  $r_x$  and  $r_{\Pi}$

Thus the DC gain is now given by

$$A_{M} = -\frac{r_{\pi}}{R_{sig} + r_{x} + r_{\pi}} (g_{m}R_{L}')$$

Using Millers theorem we obtain

$$C_{\rm in} = C_{\pi} + C_{\mu} (1 + g_m R_L')$$

Correspondingly, the 3-dB frequency  $f_{\rm H}$  can be estimated from

$$f_{II} \cong \frac{1}{2\pi C_{\rm in} R_{\rm sig}'}$$

Alternatively, using the method of open-circuit time constants yields

$$\begin{aligned} \tau_{H} &= C_{\pi} R_{\pi} + C_{\mu} R_{\mu} + C_{L} C_{C_{L}} \\ &= C_{\pi} R_{\text{sig}}' + C_{\mu} [(1 + g_{m} R_{L}') R_{\text{sig}}' + R_{L}'] + C_{L} R_{L}' \end{aligned}$$

from which  $f_H$  can be estimated as

$$f_H \cong \frac{1}{2\pi\tau_H}$$

The exact analysis yields the following zero frequency:

$$f_Z = \frac{1}{2\pi} \frac{g_m}{C_\mu}$$

and, assuming that a dominant pole exists

$$f_{P_1} = \frac{1}{2\pi} \frac{1}{[C_{\pi} + C_{\mu} (1 + g_m R'_L)] R'_{\text{sig}} + (C_L + C_{\mu}) R'_L}$$

$$f_{P_2} = \frac{1}{2\pi} \frac{[C_{\pi} + C_{\mu} (1 + g_m R'_L)] R'_{\text{sig}} + (C_L + C_{\mu}) R'_L}{[C_{\pi} (C_L + C_{\mu}) + C_L C_{\mu}] R'_{\text{sig}} R'_L}$$

For  $f_Z, f_{P_2} \ge f_{P_1}$ ,

$f_H \cong f_{P1}$

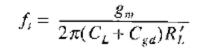

#### 2.3.5 The Situation When R<sub>sig</sub> Low

There are applications in which the CS amplifier is fed with a low-resistance signal source. Obviously, in such a case, the high-frequency gain will no longer be limited by the interaction

of the source resistance and the input capacitance. Rather, the high-frequency limitation happens at the amplifier output, as we shall now show.

The high-frequency equivalent circuit of the common-source amplifier in the limiting case when  $R_{sig}$  is zero. The voltage transfer function V<sub>0</sub> / V sig = *Vo*/*Vgs* can be found by setting  $R_{sig} = 0$  The result is

$$\frac{V_o}{V_{\rm sig}} = \frac{(-g_m R_L')[1 - s(C_{gd}/g_m)]}{1 + s(C_L + C_{gd})R_L'}$$

Thus, while the dc gain and the frequency of the zero do not change, the high-frequency response is now determined by a pole formed by CL + Cgd together with R'L. Thus the 3-dB frequency is now given by

$$f_H = \frac{1}{2\pi (C_L + C_{gd})R'_L}$$

Observe that the circuit reduces to a capacitance (CL + Cgd) in parallel with a resistance  $R'_L$ .

As we have seen above, the transfer-function zero is usually at a very high frequency and thus does not play a significant role in shaping the high-frequency response. The gain of the CS amplifier will therefore fall off at a rate of - 6 dB/octave (- 20 dB/decade) and reaches unity (0 dB) at a frequency  $f_t$ , which is equal to the gain - bandwidth product,

$$f_t = |A_M| f_H$$

$$= g_m R'_L \frac{1}{2\pi (C_L + C_{gd}) R'_L}$$

Thus,

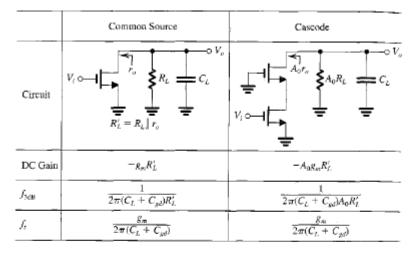

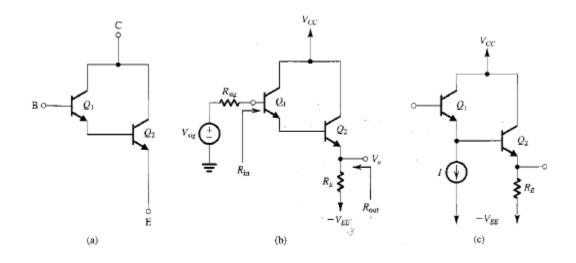

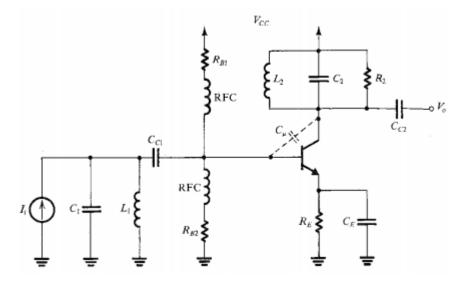

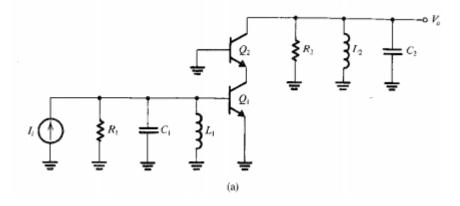

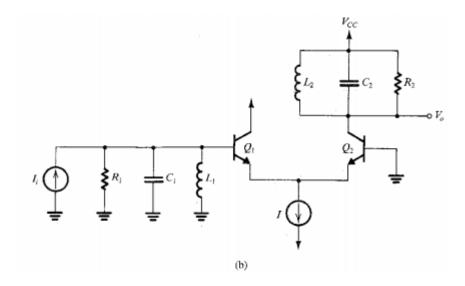

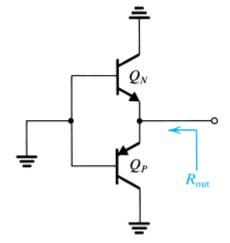

**2.4 THE CASCODE AMPLIFIER:** The Cascode Amplifier, The MOS Cascode, Frequency Response of the MOS Cascode, The BIT Cascode, Darlington configuration

## **2.4 THE CASCODE AMPLIFIER**

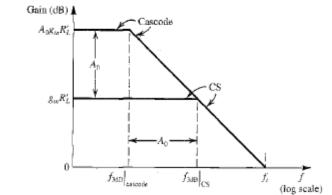

By placing a common-gate (common-base) amplifier stage in cascade with a common-source (common-emitter) amplifier stage, a very useful and versatile amplifier circuit results. It is known as the cascode configuration and has been in use for nearly three quarters of a century, obviously in a wide variety of technologies.

The basic idea behind the cascode amplifier is to combine the high input resistance and large trans conductance achieved in a common-source (common-emitter) amplifier with the current-buffering property and the superior high-frequency response of the common-gate (common-base) circuit. As will be seen shortly, the cascode amplifier can be designed to obtain a wider bandwidth but equal dc gain as compared to the common-source (common emitter) amplifier. Alternatively, it can be designed to increase the dc gain while leaving the gain-bandwidth product unchanged. Of course, there is a continuum of possibilities between these two extremes.

Although the cascode amplifier is formed by cascading two amplifier stages, in many applications it is thought of and treated as a single-stage amplifier.

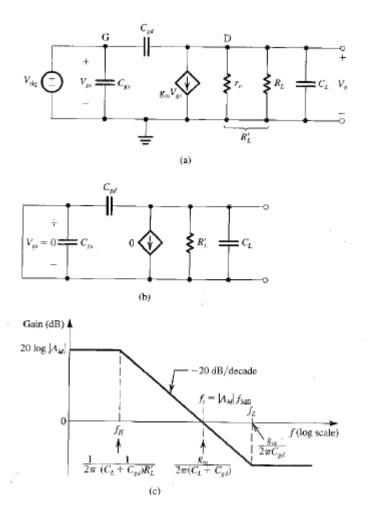

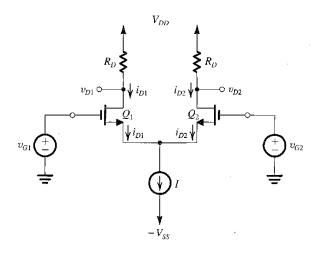

# 2.4.1 The MOS Cascode

a) The MOS cascode amplifier, (b) The circuit prepared for small-signal analysis with various input and output resistances indicated, (c) The cascode with the output open-circuited.

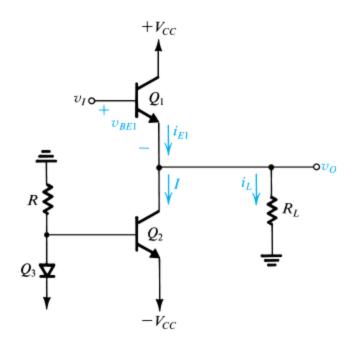

Above Figure (a) shows the MOS cascode amplifier. Here transistor Q1 is connected in the common-source configuration and provides its output to the input terminal (i.e., source) of transistor Q2. Transistor Q2 has a constant dc voltage,  $V_{BIAS}$ , applied to its gate. Thus the signal voltage at the gate of Q2 is zero, and Q2 is operating as a CG amplifier with a constant current load I. Obviously both Q1 and Q2 will be operating at dc drain currents equal to I. As in previous cases, feedback in the overall circuit that incorporates the cascode amplifier establishes an appropriate dc voltage at the gate of Q1 so that its drain current is equal to I. Also, the value of V <sub>BIAS</sub> has to be chosen so that both Q1 and Q2 operate in the saturation region at all times.

**Small-Signal Analysis** We begin with a qualitative description of the operation of the cascode circuit. In response to the input signal voltage  $v_i$  the common-source transistor Q1 conducts a current signal  $g_{m1}v_i$  in its drain terminal and feeds it to the source terminal of the common-gate transistor Q2, called the cascode transistor. Transistor Q2 passes the signal current  $g_{m1}v_i$  on to its drain, where it is supplied to a load resistance  $\mathbf{R}_L$  at a very high output resistance,  $\mathbf{R}$  out. The cascode transistor Q2

acts in effect as a buffer, presenting a low input resistance to t he drain of Q1 and providing a high resistance at the amplifier output.

Next we analyze the cascode amplifier circuit to determine its characteristic parameters. Toward that end Fig. (b) shows the cascode circuit prepared for small-signal analysis and with a resistance  $R_L$  shown at the output.  $R_L$  is assumed to include the output resistance of current source I as well as an actual load resistance, if any. The diagram also indicates various input and output resistances obtained using the results of the analysis of the CS and CG amplifiers in previous sections. Note in particular that the CS transistor Q1 provides the cascode amplifier with an infinite input resistance. Also, at the drain of Q1 looking "downward," we see the output resistance of the CS transistor Q1,  $r_{01}$ . Looking "upward," we see the input resistance of the CG transistor Q2,

$R_{in2} = \frac{1}{g_{m2} + g_{mir2}} + \frac{R_L}{A_{vo2}}$

$$A_{\mu\nu2} = 1 + (g_{m2} + g_{mb2})r_{\nu2}$$

Thus the total resistance between the drain of  $Q_1$  and ground is

$$R_{d1} = r_{o1} \Downarrow \left[ \frac{1}{g_{m2} + g_{m22}} + \frac{R_L}{A_{102}} \right]$$

$$R_{out} = r_{o2} + A_{vo2} r_{o1}$$

$$R_{\text{cut}} = r_{o2} + [1 + (g_{m2} + g_{mb2})r_{o2}]r_{u1}$$

$$R_{\text{out}} \cong (g_{m2}r_{o2})r_{o1} = A_0r_{o1}$$

$$v_i = v_{sig}$$

Thus,

where

$$G_v = A_v$$

Also, note that the amplifier is unilateral; thus,

$$R_o = R_{cat}$$

$$\frac{v_{o1}}{v_i} = -g_{m1}r_{o1} = -A_{01}$$

$v_{\sigma} = A_{vo2}v_{o1}$

Thus,

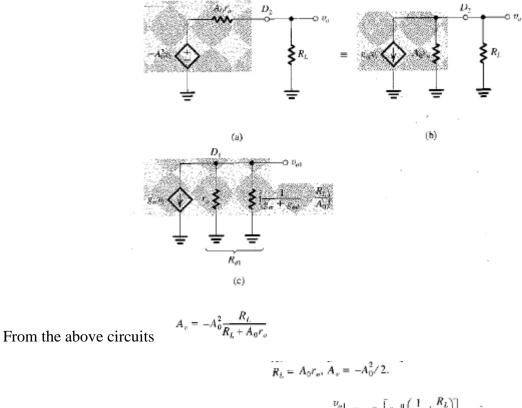

$$A_{vo} = -A_{01}A_{vo2}$$

$$\cong -A_{01}A_{02}$$

which for the usual case of equal intrinsic gains becomes

$$A_{m_{\nu}} = -A_0^2 = -(g_m r_o)^2$$

$$A_{vo} = -G_m R_o$$

$$G_m = \frac{A_{01} A_{vo2}}{r_{o2} + A_{oo2} r_{o1}}$$

$$= \frac{g_{m1} r_{o1} [1 + (g_{m2} + g_{mb2}) r_{o2}]}{r_{o2} + [1 + (g_{m2} + g_{mb2}) r_{o2}] r_{o1}}$$

$$= g_{m1}$$

$\approx g_{m1}$

The operation of the cascode amplifier should now be apparent: In response to V<sub>i</sub> the CS transistor provides a drain current  $gm_1V_i$ , which the CG transistor passes on to  $R_L$  and, in the process, increases the output resistance by A<sub>0</sub>. It is the increase in Rout to A<sub>0</sub>r<sub>0</sub> that increases the open-circuit voltage gain to  $(gm)(A_0r_0) = A_0^2$

$$\begin{aligned} \frac{v_{o1}}{v_i} &= -g_m \left[ r_o \, \| \left( \frac{1}{g_m} + \frac{R_L}{A_0} \right) \right] \\ &= -g_o \left[ r_o \, \| \left( \frac{1}{g_m} + r_o \right) \right] \\ &\equiv -\frac{1}{2} g_m r_o = -\frac{1}{2} A_0 \end{aligned}$$

$$\begin{aligned} \frac{v_{o1}}{v_i} &= -g_m \left[ r_o \, \| \left( \frac{1}{g_m} + \frac{1}{g_m} \right) \right] \\ &\equiv -2 \, \nabla/\nabla \end{aligned}$$

$$A_v &= -A_0^2 \frac{r_o}{r_o + A_0 r_o} \equiv -A_0 \end{aligned}$$

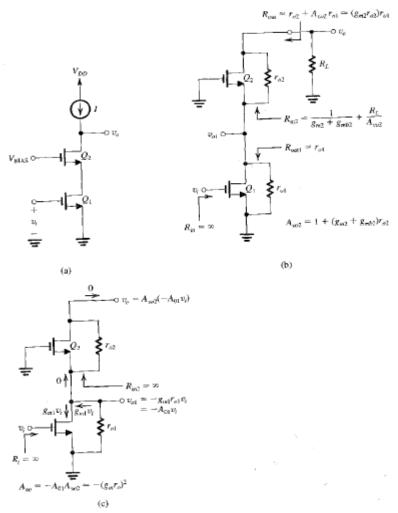

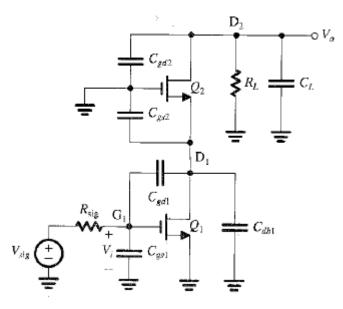

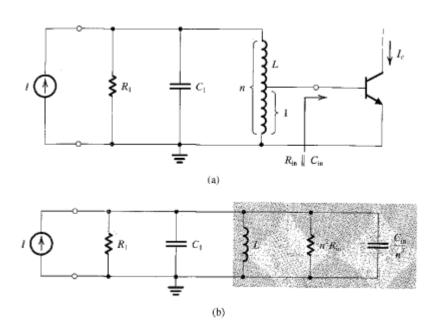

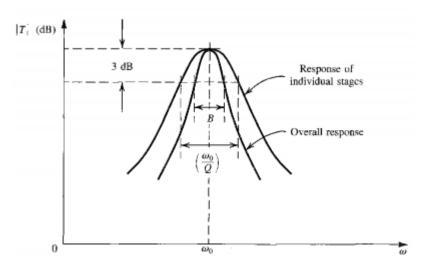

2.4.2 Frequency Response of the MOS Cascode

Above Figure shows the cascode amplifier with all transistor internal capacitances indicated. Also included is a capacitance  $C_L$  at the output node to represent the combination of  $C_{db2}$ , the input capacitance of a succeeding amplifier stage (if any), and a load capacitance (if any). Note that  $C_{db1}$  and  $C_{gs2}$  appear in parallel, and we shall combine them in the following analysis. Similarly,  $C_L$  and  $C_{gd2}$  appear in parallel and will be combined.

- 1. Capacitance  $C_{gs1}$  sees a resistance  $R_{sig}$ .

- 2. Capacitance C<sub>gdl</sub> sees a resistance R<sub>gdl</sub>, which can be obtained by adapting the formula

$$R_{gd1} = (1 + g_{m1}R_{d1})R_{sig} + R_{d1}$$

3.Capacitance  $(C_{dbl} + C_{gs2})$  sees a resistance  $R_{dl}$ .

4. Capacitance  $(C_L + R_{gd2})$  sees a resistance  $(R_L \setminus R_{out})$ .

With the resistances determined, the effective time constant  $\tau_H$  can be computed as